基于CS5460A的智能電力控制系統

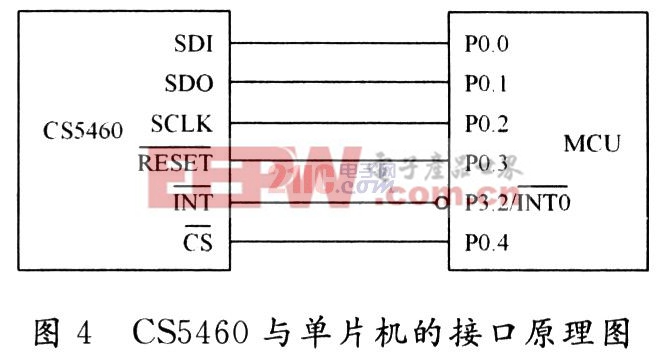

CS5460A的數據輸入SDI、數據輸出SDO、串行時鐘SCLK、片選、分別MCU與MC的PO.0,P0.1,P0.2,P0.4相連,復位端RESET接P89C61X2的PO.3,測量之前要對CS5460A進行復位。

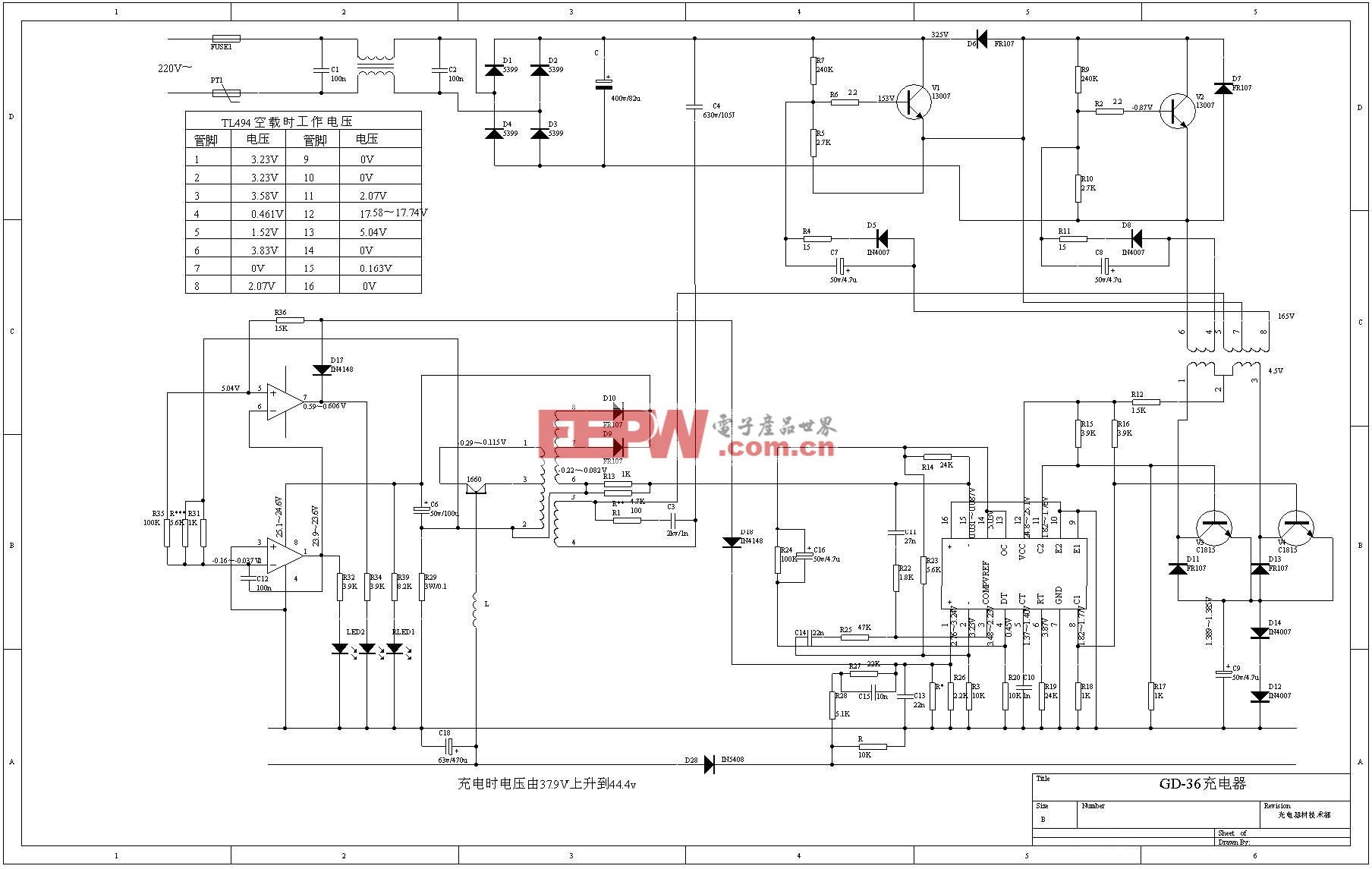

引腳用來通知系統轉換器轉換結束或出錯信息,這些事件包括芯片運行的狀態和內部故障狀態,與P89C61X2的INT0相連,低電平有效。狀態寄存器與屏蔽寄存器組合將產生信號,當狀態寄存器的某位有效,并且屏蔽寄存器相應的位是邏輯1,INT信號被激活;當狀態寄存器的這一位恢復為無效時,中斷狀態被清除,一般89C51每經一次計算周期通過中斷或查詢讀一次測量數據。CS5460A與89C51系列單片機的接口電路如圖4所示。本文引用地址:http://www.104case.com/article/163192.htm

1.4 時鐘模塊的接口設計

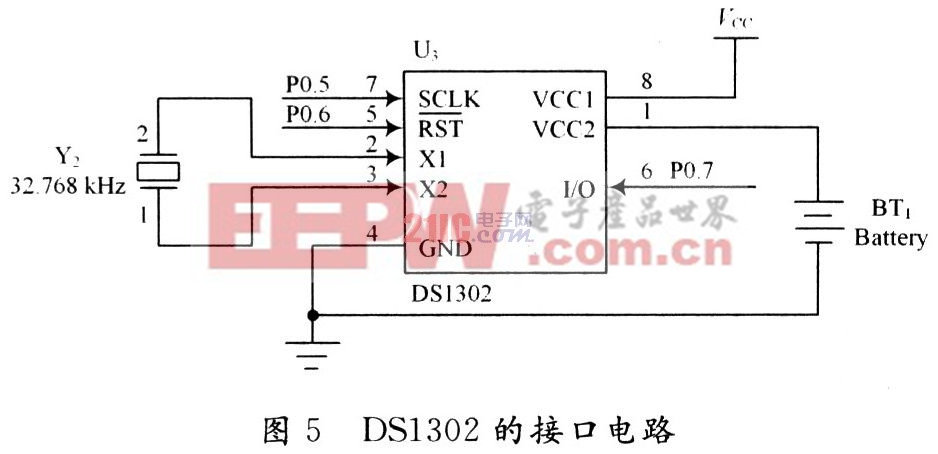

DS1302是DALLAS公司推出的涓流充電時鐘芯片內含有一個實時時鐘/日歷和31字節靜態RAM通過簡單的串行接口與單片機進行通信實時時鐘/日歷電路提供秒分時日日期月年的信息每月的天數和閏年的天數可自動調整時鐘操作可通過AM/PM指示決定采用24或12小時格式DS1302與單片機之間能簡單地采用同步串行的方式進行通信僅需用到三個口線:RST復位端;I/0數據線;SCLK串行時鐘時鐘。RAM的讀/寫數據以一個字節或多達31個字節的字符組方式通信。 DS1302工作時功耗很低保持數據和時鐘信息時功率小于1 mW。其接口電路如圖5所示。

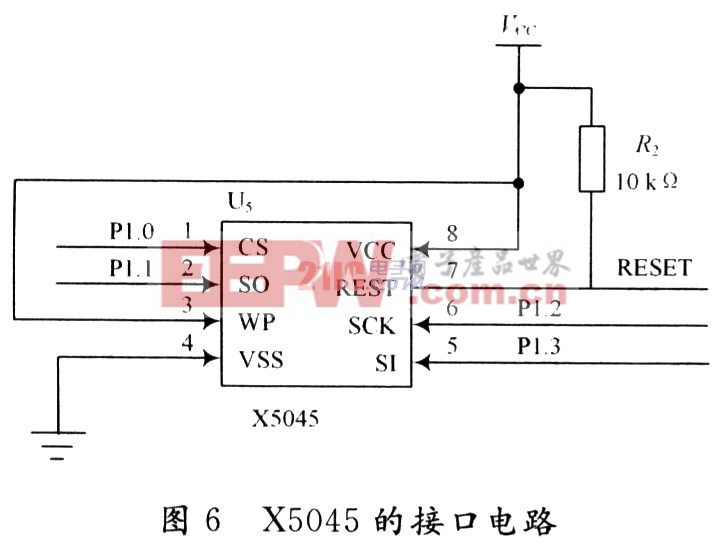

1.5 E2PROM模塊的接口設計

該芯片內的串行E2PROM是具有Xicor公司塊鎖的保護功能的CMOS串行E2PROM,它被組織成8位結構,由一個四線構成的SPI總線方式進行操作,其擦寫次數至少有l 000 000次,并且能保存數據長達100年。X5045的接口電路如圖6所示。

1.6 ZLG500C的接口設計

為了能減少I/0口的占用,提高系統的集成度,本系統采用ZLG500C讀卡器模塊來進行開發。ZLG500C以MFRC500為主體,該系列模塊具有如下特點:四層電路板設計,雙面表貼工藝,EMC性能優良;采用PHILIPs高集成度讀卡芯片MFRC500;具有控制線和可控蜂鳴器信號輸出;能讀寫MFRC500內E2PROM;支持Mifarel S50,Mifarel S70,MifareUltraLight,Mifare Light。

在使用時只需將Rx,Tx和相應控制接口接入MAX485的相應端口即可,模塊中所具有的微控制器能根據特定的數據格式,進行網絡層和數據鏈路層的格式轉換,使得ZLG500C和單片機之間進行通訊。

2 系統軟件設計

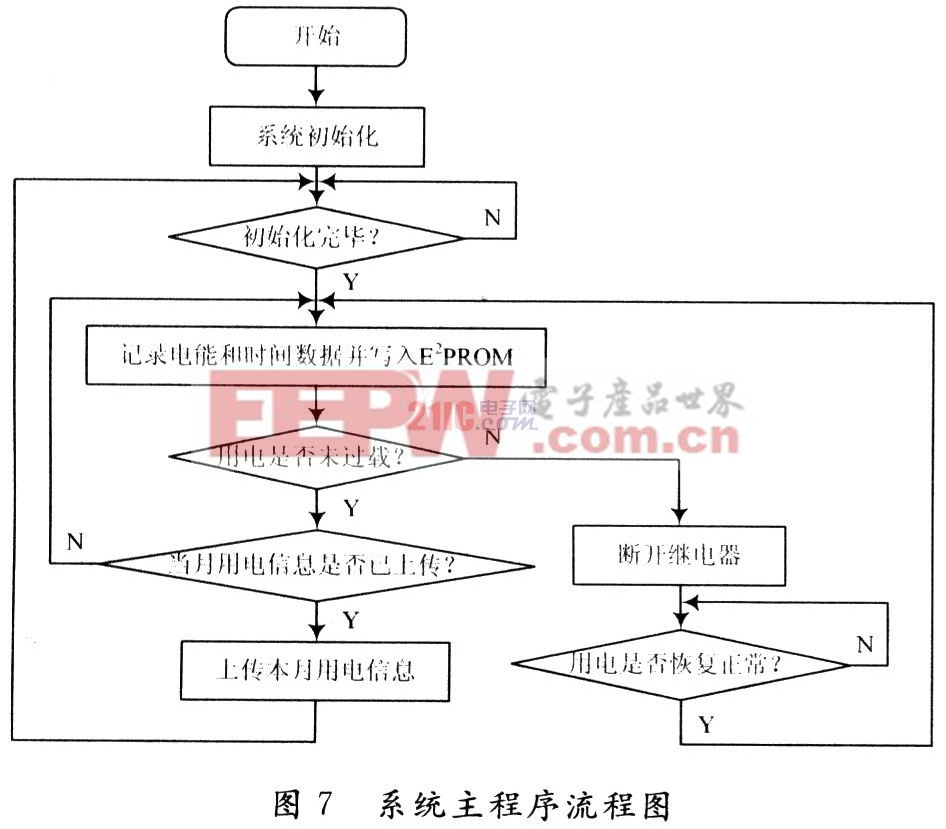

2.1 系統主體程序框架設計

整個系統軟件由主程序與數據采集子程序、數據記錄子程序、數據通信子程序、異常處理子程序、顯示子程序等組成。如圖7所示。

評論