基于C167的PROFlBUS-DP智能從站的設計

摘要:設計了基于C167的PROFIBUS-DP總線協議的智能從站。依據系統所要實現的功能,提出了使用PRO-FIBUS-DP協議智能接口芯片SPC3和軟件的實現方案。以C167與SPC3為核心設計了其軟硬件系統,經調試滿足了設計要求,目前已在實際工程中得到應用。

關鍵詞:PROFIBUS-DP;智能從站;C167;SPC3

現場總線控制系統已逐漸發展成為繼集散控制系統之后的新一代控制系統,在眾多的現場總線標準中,過程現場總線(PROFIBUS)標準以其國際化、開放式、不依賴設備生產商的種種優勢,成為當前爭相研究的對象。

PROFIBUS廣泛適用于制造業自動化、流程工業自動化和樓宇、交通電力等領域的自動化,是一種用于工廠自動化車間級監控和現場設備層數據通信與控制的現場總線技術。可實現現場設備層到車間級監控的分散式數字控制和現場通信網絡,從而為實現工廠綜合自動化和現場設備智能化提供了可行的解決方案。

與其它現場總線系統相比,PROFIBUS的優勢在于具有穩定的國際標準EN50170作保證,并經實際應用驗證其具有普遍性。目前已應用的領域包括加工制造、過程控制和自動化等。PROFIBUS-DP是開放的,與制造商無關,無知識產權保護的標準。任何人都可以獲得這個標準并設計各自的軟硬件方案。原則上,PROFIBUS-DP協議在任何微處理機器上都可以實現,在微處理器內部或外部安裝串行通信接口即可完成。利用PROFIBUS-DP模型中的服務訪問點,通過單片機編程來實現PROFIBUS-DP的狀態機制。

PROFIBUS協議結構是根據IS07498國際標準,以開放式系統互聯網絡(Open System Interconnection-OSI)作為參考模型的。該模型共有7層,文中所探討的PROFIBUS-DP系統定義了第1,2層和用戶接口。使用單片機C167和智能通訊芯片SPC3設計了PROFIBUS-DP智能從站的硬件電路及其控制軟件,該系統即將在西北電網與華北電網聯網的靈寶背靠背直流工程中投入使用。

1 PROFIBUS-DP系統配置和設備類型

PROFIBUS-DP允許構成單主站或多主站系統。在同一總線上最多可連接126個站點。系統配置的描述包括:站數、站地址、輸入/輸出地址、輸入/輸出數據格式、診斷信息格式及所使用的總線參數。每個PROFIBUS-DP系統可包括以下幾種不同類型設備:

(1)一級DP主站(DPM1):一級DP主站是中央控制器,它在預定的信息周期內與分散的站(如DP從站)交換信息,典型的DPM1如PLC或PC;

(2)二級DP主站(DPM2):二級DP主站是編程器、組態設備或操作面板,在DP系統組態操作時使用,完成系統操作和監視目的;

(3)DP從站:DP從站是進行輸入和輸出信息采集和發送的外圍設備(I/O設備、驅動器、HMI、閥門等);

(4)單主站系統:在總線系統的運行階段,只有一個活動主站;

(5)多主站系統:總線上連有多個主站。這些主站與各自從站構成相互獨立的子系統。每個子系統包括一個DPM1、指定的若干從站及可能的DPM2設備。

任何一個主站均可讀取DP從站的輸入/輸出映象,但只有一個DP主站允許對DP從站寫入數據。

DPM1和相關DP從站之間的用戶數據傳輸是由DPM1按照確定的遞歸順序自動進行。在對總線系統進行組態時,用戶對DP從站與DPM1的關系作出規定,確定哪些DP從站被納入信息交換的循環周期,哪些被排斥在外。

DPM1和DP從站間的數據傳送分3個階段:參數設定、組態、數據交換。在參數設定階段,每個從站將自己的實際組態數據與從DPM1接收到的組態數據進行比較。只有當實際數據與所需的組態數據相匹配時,DP從站才進入用戶數據傳輸階段。因此,設備類型、數據格式、長度以及輸入輸出數量必須與實際組態一致。

2 電路主要器件介紹

從站的硬件電路采用西門子C167單片機和智能通訊芯片SPC3。

2.1 C167微控制芯片

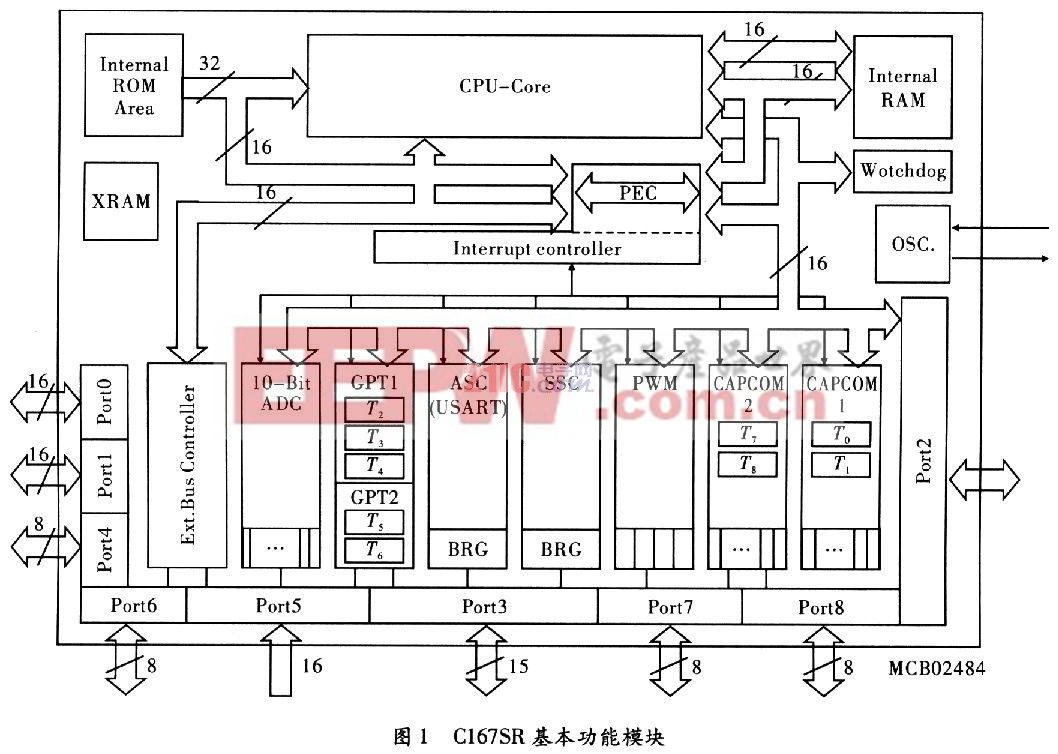

C167SR是西門子C16X系列第二代CMOS微處理器。它兼容16位CPU的高性能(高達1 000萬條指令每秒),并具有智能外圍設備擴展功能。它的主要優點體現在:增強了IO口的應用,提供了附加的內部高速RAM,CAN總線控制器和鎖相環PLL等功能;繼承了RISC處理器的優點,而克服了CISC處理器在嵌入式應用中的瓶頸;在指令處理上,采用4級指令流水線管道結構;在存儲管理上,統一線性地址空間可達16 MB,具有段代碼、頁數據式管理機制;采用寄存器池,池間的切換時間只要80 ns;16位乘法400 ns,32位除法800 ns,中斷響應時間最長400 ns;外部事件控制器PEC服務具有類似DMA的功能,可實現存儲器與外設之間的高速數據傳輸;豐富的在片外設:2 kB RAM、10路A/D、111路I/O、5個定時器/計數器、16個比較/捕獲單元、2個串行通信接口、在片的Watchdog等。

CPU的內核是由一個4級流水線指令管道,一個16位的算術邏輯單元以及指示作用的SFR構成。另外還專有做乘法,除法運算的硬件單元,一個位屏蔽器,一個移位器。基于這些硬件保證,大多數C167的指令在20 MHz時鐘頻率下,只需要1個時鐘周期,也就是100 ns就能完成。例如,移位和循環指令通常只要一個時鐘周期,而和移位的數目沒關系。被優化的乘除法指令使得執行速度快了很多,它分成了2個部分:16×16位的乘法需要5個周期,32/16位的除法需要10個周期。另一個管道優化,即所謂的跳緩存,它將重復的循環跳轉指令周期由2個減到1個。CPU可以對位于片上RAM的特殊寄存器進行16位的直接處理。CPU每訪問一次寄存器組,其基址由索引指針寄存器指定。寄存器組數目僅僅受限于內部RAM的可用空間。對于簡單的參數傳遞,一組寄存器可能會覆蓋其它數據。最高達2 kB的系統堆棧用來存儲臨時數據。此堆棧也是位于片上RAM,CPU對其通過堆棧指針寄存器進行訪問。兩個獨立的特殊功能寄存器,STKOV以及STKUN,通過比較堆棧內的值來檢測被訪問的堆棧是否上溢和下溢,其基本功能模塊,如圖l所示。

評論