16位微控制器的設(shè)計與實現(xiàn)

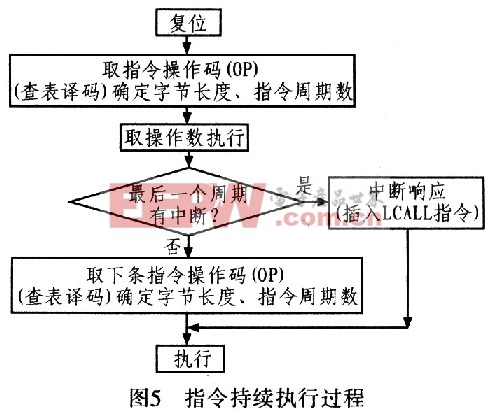

需要說明:codefetche為取操作碼信號,datafetche為取操作數(shù)信號。在指令最后一個周期時若有中斷請求,則插入LCALL指令進(jìn)行中斷處理,讀取下一條指令。其流程如圖5所示。本文引用地址:http://www.104case.com/article/162885.htm

2.4 指令譯碼過程

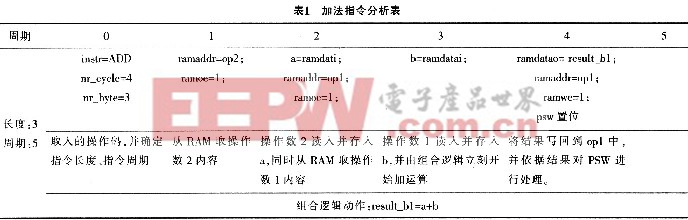

在MCU設(shè)計過程中,首先完成對各條指令的指令分析工作,確定每個周期該做的動作,然后各部件依據(jù)指令分析表進(jìn)行相關(guān)的指令譯碼(RAM控制器只譯RAM要做的動作,ALU只譯ALU要做的動作)。過程描述如下:在預(yù)取操作碼時,CU單元對操作碼進(jìn)行譯碼確定指令的字節(jié)長度(nr_bytes)和指令周期數(shù)(nr_cycles)。然后CU依據(jù)指令字節(jié)長度(nr_bytes)取操作數(shù),其他部件依據(jù)指令和當(dāng)前指令周期(curcycle)執(zhí)行相應(yīng)的指令操作。表1為加法指令分析表,下面以加法指令的譯碼過程來說明整個譯碼流程:

1)加法指令 ADD OPl OP2(將OPl+0P2結(jié)果寫入OPl中);其目標(biāo)碼格式為:ADD OP2 OPl,其中OPl和OP2均為操作數(shù)地址。

2)0周期 實際指上一條指令的最后一個時鐘周期,此周期codefetche取指信號有效,IPU單元將指令送入CU單元確定了指令周期和指令長度。

3)l周期 取操作數(shù)信號datafetche有效,op2(地址)進(jìn)來,被送入RAM地址線,發(fā)讀信號(從RAM寄存器陣列取操作數(shù)2)。

4)2周期 操作數(shù)2被取入,并存入ALU中的a寄存器;此周期取操作數(shù)信號datafetche有效,opl(地址)進(jìn)來,被送入RAM地址線,發(fā)讀信號。

5)3周期 操作數(shù)l被取入,并存入ALU中的b寄存器;加法器立刻進(jìn)行a+b運(yùn)算。

6)4周期 將加法結(jié)果放到RAM數(shù)據(jù)線上,地址線=opl,發(fā)寫信號。將加法結(jié)果寫回到opl中,并依據(jù)結(jié)果對PSW進(jìn)行處理。

7)5周期 無動作,用于寫回操作的過程。

3 驗證結(jié)果

3.1 仿真驗證

芯片的功能與結(jié)構(gòu)設(shè)計,只是設(shè)計流程的一部分,為保證最終設(shè)計成功,必須對其全面仿真與功能驗證。對MCU的測試方法如下:1)功能模塊的單元測試,驗證模塊的功能正確性,包括接口時序等。2)系統(tǒng)集成測試,首先編寫簡單的機(jī)器碼測試向量進(jìn)行初步調(diào)試:然后使用編譯器寫匯編程序,編譯成二進(jìn)制機(jī)器碼進(jìn)行程序功能測試。在集成測試中,編寫匯編測試程序,用編譯器編譯成機(jī)器碼,在Cadenee NC下運(yùn)行這些測試程序進(jìn)行仿真測試。對每條指令均測試了其各種尋址方式,且測試程序自動向DEBUG寄存器寫測試結(jié)果,以方便調(diào)試。經(jīng)過復(fù)雜的測試和不斷修正,驗證結(jié)果顯示MCU指令執(zhí)行的正確性。

3.2 FPGA驗證

使用的FPGA器件是StratixⅡ型號為EP1S40F780C7。綜合結(jié)果顯示:A8096使用3 565個LE(Logic Element)。時序分析結(jié)果:A8096可以運(yùn)行在49.93 MHz的時鐘頻率下。A8096占用FPGA資源分布情況如圖6所示。

4 結(jié)論

本設(shè)計中,采用RISC技術(shù)中的硬布線控制邏輯,有利于減少M(fèi)CU面積、降低功耗以及提高M(jìn)CU執(zhí)行效率,F(xiàn)PGA實現(xiàn)表明其只占用了3 565個LE單元,工作時鐘可達(dá)50 MHz。同時該MCU具有很強(qiáng)的擴(kuò)展性與實用性,應(yīng)用領(lǐng)域廣泛,可方便與定時器、串行通訊接口(I2C)、串行外圍接口(SPI)、模數(shù)(A/D)轉(zhuǎn)換器等外圍功能單元組成各種嵌入式系統(tǒng),完全具備實際應(yīng)用價值。

評論