可編程微波爐控制器的設計

2.4 計數器counter的設計

根據設計要求,counter為減數計數器,其最大計時99:59。因此可以用3個十進制計數器和1個六進制計數器級聯構成。計數器的工作與狀態機的狀態有關,當狀態機處在復位狀態、測試狀態、停止狀態、結束狀態、檔位狀態都屬于不工作狀態,只有在計數狀態時,才會工作。計數器如果進入了停止狀態,會保留當前計數值,當再次按下開始鍵時,計數器由當前值開始計數。

4個計數器的計數使能端相連、置數使能端相連,實現同時計數和同時置數。第一個計數器的計數脈沖是從1 kHz輸入的,第二個計數器的計數脈沖clk與第一個計數器的進位cn相連,第三個計數器的計數脈沖clk與第二個計數器的進位相連cn,第四個計數器的計數脈沖clk與第三個計數器的進位cn相連,設計中使用了庫中的一個4輸入與門,所有進位輸出都連接到4輸入與門,當倒計時結束,done輸出“1”信號。

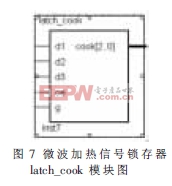

2.5 微波加熱信號鎖存器latch_cook的設計

對于latch_cook的設計,主要用來鎖存微波信號,數據的輸入由狀態控制得到,當啟動檔位1時,st1_en輸出信號為1、st1_en輸出信號為0、st1_en輸出信號為0,1_en與d1相連、 st2_en與d2相連、 st3_en與d3相連,也就是d1d2d3輸入端口的數據是啟動檔位1的輸出數據“001”。同理,當啟動檔2時,d1d2d3輸入端口的數據為“010”,啟動檔位3時,d1d2d3輸入端口的數據為“011”,其他狀態時latch_cook模塊設計中使用了兩個進程。第一個進程是把輸入微波信號賦給寄存器q,當g使能信號為1時,判斷是哪個檔位微波加熱信號后,再對寄存器q進行賦值。使能端g是從load_en取得信號值的。輸出load_en為1信號只有復位、測試、結束、檔位這幾個工作狀態。其中只有在檔位狀態時才能觸發進程,其他都不能。第二個進程是對微波信號的鎖存控制,eo與計數使能端相連,只有在計數時才能觸發進程,使cook輸出信號值,否則cook輸出高阻抗信號。latch_cook的輸入、輸出端口如圖7所示。

部分關鍵程序如下:

architecture one of latch_cook is

signal q:std_logic_vector(2 downto 0);

signal s:std_logic_vector(2 downto 0);

begin

s=d1d2d3;

process(s)

begin

if g='1'then

case s is

when001=>q=001;--檔位3

when010=>q=010;--檔位2

when100=>q=100;--檔位1

when others=>null;

end case;

end if;

end process;

process(oe)

begin

if oe='1'then--輸出信號

cook=q;

else

cook=ZZZ;--呈現高阻抗

end if;

end process;

end;

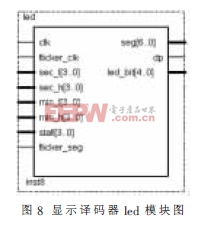

2.6 顯示譯碼器LED的設計

對于顯示電路,硬件上使用了串行連接的設計,即每個數碼管對應的引腳都接在一起,通過控制公共端控制相應數碼管的亮滅(共陰極數碼管的公共端為高電平時,LED不亮;共陽極的公共端為低電平時,LED不亮)。

因此,在顯示模塊里有4個進程實現設計——數碼管動態掃描計數進程、數碼管位動態掃描進程、數碼管閃爍顯示進程、譯碼信號進程。顯示模塊工作首先是動態掃描計數,以1 kHz的掃描頻率進行掃描計數。掃描所得到的計數值傳遞到數碼管位動態掃描進程中,控制數碼管的位選信號,即顯示完第一位后,接著顯示第二位,依此類推,一直顯示到第5位,顯示模塊接著繼續從第一位顯示,從而實現循環顯示。因為1 kHz的掃描頻率使6個數碼管看上去是同時顯示的,實現了計數結果和狀態信息的顯示;譯碼信號進程則根據動態掃描所得到的信號值,選擇相應的顯示數據,只要計數器數據輸出或狀態發生變化,則數碼管的顯示也發生相應的變化。對于數碼管閃爍顯示進程,當ficker_seg=1時,則段信號與1 Hz頻率相與后再送到輸出端去以1 s的頻率閃爍、一亮一暗、全段滅、全段亮,否則正常輸出段信號。顯示模塊的輸入、輸出端口如圖8所示。

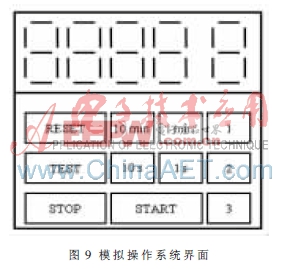

3 系統調試

為了能夠準確地對所編寫的軟件進行調試,采用EMP240系列開發板上進行系統調試。圖9是一個模擬操作系統界面。

系統調試的主要步驟如下:

(1) 在上電復位時,系統操作界面顯示:00000。微波加熱信號為0。正處于待機狀態。

(2)按下TEST測試鍵,5個數碼管所有段位點亮同時一亮一暗地交替閃爍著。按下復位鍵,系統返回復位待機狀態。

(3) 右邊有三個檔位控制鍵,在待機狀態時,只要按下其中一個鍵,就能對時間進行設定。而三個檔位之間可以相互轉換。按下復位鍵,系統返回復位待機狀態。

(4) 設定好時間后就可以按下開始鍵,啟動相應微波加熱信號,同時進行倒計時計數,如果要停止加熱,則按下停止鍵,系統進入停止狀態,微波加熱信號輸出為0,想要再次加熱,則按回開始鍵。按下復位鍵,系統返回復位待機狀態。

(5) 當計時結束后,輸出done顯示提示,微波加熱信號輸出為0。按下復位鍵,系統返回復位待機狀態。

本系統以EMP240T100C5為主要控制芯片,綜合運用了Quartus II開發工具,使用VHDL硬件描述語言,使得系統設計的硬件功能基本都可以通過軟件編程實現,程序經過實驗仿真與調試,各項功能達到了預定的設計指標。這種設計方案不僅使電子系統的設計以及產品性能的改進和擴展變得十分簡單,同時它還代替了原有的許多單元電路或單片機的控制芯片和大量外圍電路,使電子電路設計更加靈活方便。為實現微波爐以及更多家用電器的信息化和智能化進行了較深入的探索和實踐。

參考文獻

[1] 周潤景,圖雅,張麗敏. 基于QuartusII的FPGA/CPLD數字系統設計實例[M]. 北京:電子工業出版社,2007.

[2] 延明,張亦華. 數字電路EDA技術入門[M].北京:北京郵電大學出版社,2006.

[3] 韓團軍. 基于FPGA微波爐控制器設計[J].研究與開發, 2010,29(8):64-67.

[4] 劉昌華. 數字邏輯EDA設計與實踐—MAX+plusII與QuartusII雙劍合璧[M].北京:國防工業出版社,2006.

西門子plc相關文章:西門子plc視頻教程

分頻器相關文章:分頻器原理

評論