M4K塊移位寄存器數據讀進方式的邏輯分析儀設計

3 控制模塊

通過FPGA內部的M4K塊配置移位寄存器不斷地讀進新的采樣值,數據采樣回來后先經過SDRAM放入緩存FIFO中,然后把該FIFO中的數據上傳到顯示器。該模塊的時鐘是由PLL電路對FPGA輸入的25 MHz晶振時鐘倍頻得到的。通過FPGA外部一組撥碼開關控制輸入電平為高或者低,從而設置不同的觸發(fā)和采樣模式。

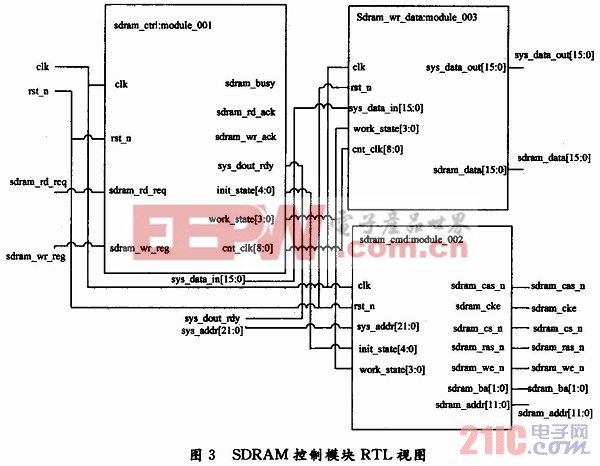

3.1 SDRAM數據存儲模塊

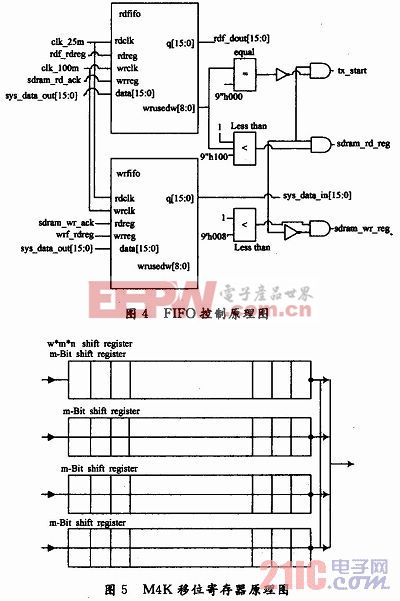

將這個存儲模塊劃分為多個子模塊來實現。如圖3所示。sdram_ctrl是SDRAM狀態(tài)控制模塊,該模塊主要完成SDRAM的上電初始化以及定時刷新、讀/寫控制等狀態(tài)的變遷。內部設計了兩個狀態(tài)機,一個用于上電初始化的狀態(tài)控制,另一個月用于正常工作時的狀態(tài)控制;sdram _cmd是SDRAM命令模塊,該模塊根據sdram_ctrl模塊的不同狀態(tài)指示輸出相應的SDRAM控制命令和地址,sdram_wr_data是SDRAM數據讀/寫模塊,該模塊同樣是根據sdram_ctrl模塊的狀態(tài)指示完成SDRAM數據總線的控制,SDRAM的數據讀/寫都在該模塊完成。數據讀/寫借助了兩個存儲器(異步FIFO)如圖4所示。其中wrfifo用于寫SDRAM數據,rdfifo用于讀SDRAM數據。在設計中SDRAM讀/寫都是以8個字(16 b)為單位,使用FIFO中的當前數據量作為操作SDRAM的狀態(tài)指示。當wrfifo數量超過8個則發(fā)出寫SD]RAM請求,讀出wrfifo中的數據。同樣,在rdfifo數據少于256 B(rd-fifo半空)時發(fā)出讀SDRAM請求,讀出8個新的數據寫入rdfifo中,以保證后續(xù)電路總是持續(xù)的傳輸。SDRAM信號采集模塊在上電延時后從SDRAM的0地址開始寫入遞增數據,隨后通過內部FIFO依次送入SDRAM。SDRAM的所有地址寫完數據后,啟動SDRAM讀邏輯,從0地址開始讀出SDRAM內的數據放入緩存FIFO中,然后把該FIFO中的數據上傳到顯示器。本文引用地址:http://www.104case.com/article/161310.htm

3.2 基于M4K的移位寄存器連續(xù)且可變頻的采樣模塊

為了實現有效效據的精確捕獲在不中斷程序運行的情況下,有效數據長時間實時讀進,提高嵌入式軟件性能分析的范圍和質量。利用Cyclone芯片內部M4K結構配置移位寄存器對數據實時采樣,并且設置2個按鍵調節(jié)控制采樣頻率。

圖5為M4K移位寄存器原理圖。配置輸入/輸出的數據位寬w,移位寄存器的一個taps位寬m,總的taps數量n。這三個參數乘積就是占用的M4K存儲大小。從圖5中可看出,每個clk輸入一個移位數據,同時輸出一個數據,而M4K內部則是每個clk周期移位一次,每個tap的輸出直接移位到下一個tap的輸入,配置后的輸出中可看到每個tap的最后一個w位寬的數據。

評論