全數字單相三電平整流器的控制電路設計

本文引用地址:http://www.104case.com/article/159732.htm

在區域1,電壓大于-ud/2,并且小于ud/2,在電壓uAB上產生三個電平:-ud/2,0,ud/2。同理,在區域2,電壓絕對值大于ud/2,并小于直流側電壓ud,在電壓正半周期(或負半周期)上產生兩個電平:ud/2和ud(或-ud/2和-ud)。相應電平的工作區域如表1所列。

表1 相應電平的工作區域 工作區域 1 2 1 2

us>0 us0 us>0 us0

高電平 ud/2 0 ud -ud/2

低電平 0 -ud/2 ud/2 -ud

SA=

(1)

SB=

(2)

根據表1可以設計一個開關查詢表,如表2所列,將其存儲在DSP中,當進行實時控制時,便可根據輸入電壓、電流信號,從表中查詢所需采取的開關策略。

表2 查詢表 SA SB V11 V12 V21 V22 V31 V32 V41 V42 uAB

1 1 1 1 0 0 1 1 0 0 0

1 0 1 1 0 0 0 1 1 0 ud/2

1 -1 1 1 0 0 0 0 1 1 ud

0 1 0 1 1 0 1 1 0 0 -ud/2

0 0 0 1 1 0 0 1 1 0 0

0 -1 0 1 1 0 0 0 1 1 ud/2

-1 1 0 0 1 1 1 1 0 0 -ud

-1 0 0 0 1 1 0 1 1 0 -ud/2

-1 -1 0 0 1 1 0 0 1 1 0

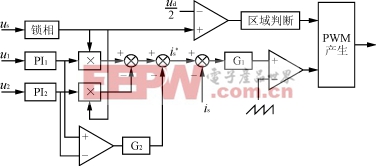

整個控制系統以一片DSP為核心,控制框圖如圖4所示。

圖4 控制框圖

鎖相環電路產生一個與電源電壓同相位的單位正弦波形,ud的采樣信號通過低速電壓外環調節器進行調節,電流is的采樣信號通過高速電流內環G1進行調節,電容C1端直流電壓u1與電容C2端直流電壓u2分別通過兩個PI調節器進行調節,補償環G2用于補償兩只電容電壓的不平衡。

檢測的線電流命令is與參考電流is*比較,產生的電流誤差信號送至電流內環G1,以跟蹤電源電流變化,產生的線電流波形將與主電壓同相位。

3 軟件設計

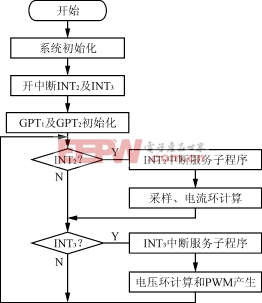

系統采用兩個通用定時器GPT1及GPT2來產生周期性的CPU中斷,其中GPT1用于PWM信號產生、ADC采樣和高頻電流環控制(20kHz),GPT2用于低頻電壓環的控制(10kHz),兩者均采用連續升/降計數模式。低速電壓環的采樣時間為100μs,高速電流環采樣時間為50μs。中斷屏蔽寄存器IMR,EVIMRA和EVIMRB使GPT1在下降沿和特定周期產生中斷,GPT2則僅在下降沿產生中斷。

整個程序分為主程序模塊、初始化模塊、電流控制環計算模塊、電壓控制環計算模塊、PWM信號產生模塊等五大部份。程序流程如圖5所示。

圖5 主程序流程

評論