基于同軸與光纖結合的2km數據傳輸的設計

摘 要:若采用沒有信號調節功能的LVDS芯片與設有驅動器預加重功能和接收器均衡功能的LVDS集成電路構成系統傳輸數據,電纜的長度便可最多到數百米。但這些系統想要進行數十公里長距離的數據傳送,便應將LVDS信號經過光模塊轉成光信號來傳輸,并將之與LNDS系統一起搭配使用。采用DS92LV1023和lDS92LV1224型號的LWDS芯片與驅動芯片CL006和CLCOl4相互配合構成LVDS系統,再與光模塊構成一個大系統便能夠傳輸數十公里的距離。該系統已投入使用,其性能可靠、穩定、支持。

關鍵詞:LVDS芯片:長距離;同軸電纜:光模塊.

0 引言

隨著各式各樣的接入通信設備的應用,數據傳輸的需求急劇增加。設備的電路系統必須提高傳輸的速度,設備采用LVDS技術,使其傳輸速度高達數百Mbps。但是,LVDS的出現只能滿足短距離(不超過幾米)傳輸條件下數據高速傳輸的要求。自適應均衡器可自動為信號損耗提供補償,使電纜傳來的串行數字信號可以重新恢復其原有強度。利用這一特點采用高速串行數字接口(SDI)自適應電纜均衡器及電纜驅動器芯片構建系統,可以擴大LVDS技術的數據傳送范圍到二、三百米。

隨著通信技術的飛速發展,光纖通信已成為通信的重要手段。光纖傳輸系統具有容量大,傳輸距離遠,抗干擾性強等優勢,在通信傳輸方面有著不可替代的地位,目前,單模光纖能以1.2Gbyte/s的速度傳輸20km。綜合以上兩個特點采用LVDS芯片與光模塊構建系統,可以在特殊環境下擴大數據傳送范圍,以滿足高速率條件下長距離傳送的要求。

在導彈上面的電纜網有好幾級托插件構成,如果用光纖接口做托插件的話需要外圍電路,并且光模塊本身體積也很大,由于導彈上的空間有限,所以在導彈上面用光纖不合理。同軸電纜則不存在這樣的問題,它通過標準SMA接插件就可以連接起來,SMA接插件比同軸電纜少粗一點,幾乎不占體積。因此,本文采用的就是高速串行數字接口(SDI)自適應電纜均衡器及電纜驅動器芯片與LVDS芯片搭配構成彈上系統,在地面上采用光模塊將LNDS信號轉成光信號傳輸2km。整個系統主要完成導彈飛行前的實時檢測過程中的數據傳輸。

1 總體方案設計

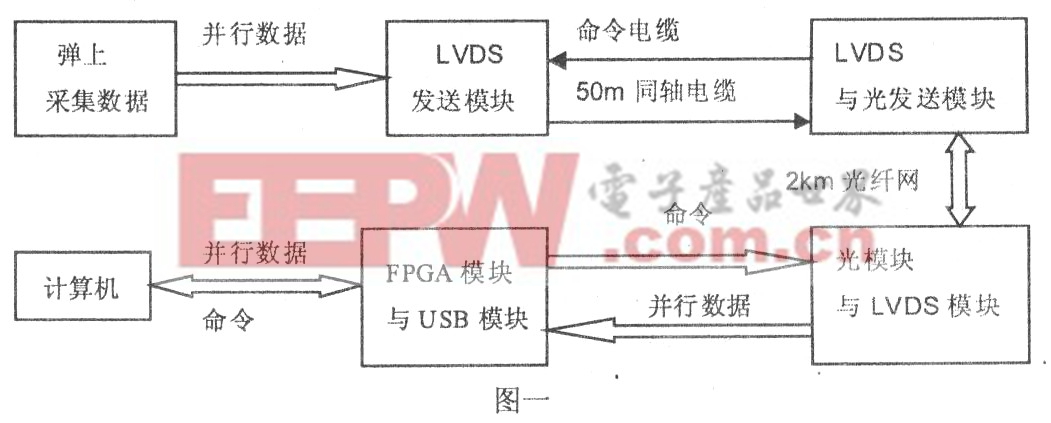

本系統需要完成在100Mbps速度情況下數據的傳輸,傳輸距離為2km。并且需要光信號與電信號的轉換問題。因此,在滿足傳輸速度為100Mbps的條件下,主要考慮的是數據的傳輸距離的問題。也就是說,需要解決兩方面的問題:(1)延長傳輸距離的問題(2)速度匹配問題。圖一為系統原理框圖。其中,導彈上的采編器采集到的數據通過LVDS發送模塊轉成串行數據,再經過50m的同軸電纜傳到地面上的LVDS模塊與光模塊組合而成的模塊,這個組合模塊是收發一體的模塊。在地面上通過收發一體的模塊將電信號轉成光信號,經過2km的光纖傳到控制室,在控制室內,又通過光模塊與LVDS模塊,將光信號轉成電平信號直接給了FPGA模塊與USB模塊。

2 硬件設計

如圖一所示,計算機與USB模塊通過USB電纜連接,計算機發給USB模塊讀數命令、啟動DS92LV1224工作命令及其他工作命令,USB模塊將命令傳給FPGA模塊,再由FPGA來直接控制LVDS芯片的工作狀態。由于本系統USB模塊傳給計算機的速度最快為140Mbps,可以將100Mbps速度的數據適時的傳到計算機里。

3 延長距離設計。

(1)彈上延長距離設計:

LVDS信號的傳輸是依靠串行器和解串器成對出現相互搭配來完成的,串行器和解串器都需要外部給它們一個工作時鐘。只有這兩個工作時鐘頻率相等,串行器和解串器之間才能正常通信。由于FPGA管腳與內部邏輯的靈活性,完全可以解決時鐘頻率相等的問題。

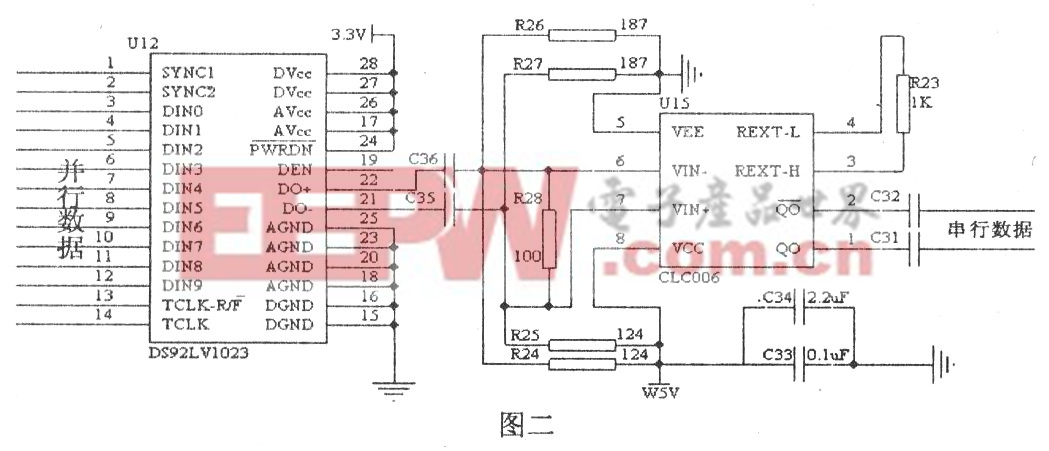

發送端:串行器DS92LV1023是將外部并行數據串化成串行數據,此時該串行器輸出的差分壓差是lOOmV左右,這種小壓差只能傳輸不到十米的距離,但加上CLC006這款電纜驅動芯片后,其輸出壓差可達到2V(壓差可通過電阻R23調節),這樣就可以驅動同軸電纜傳輸300米的距離。其部分電路圖如圖二所示。

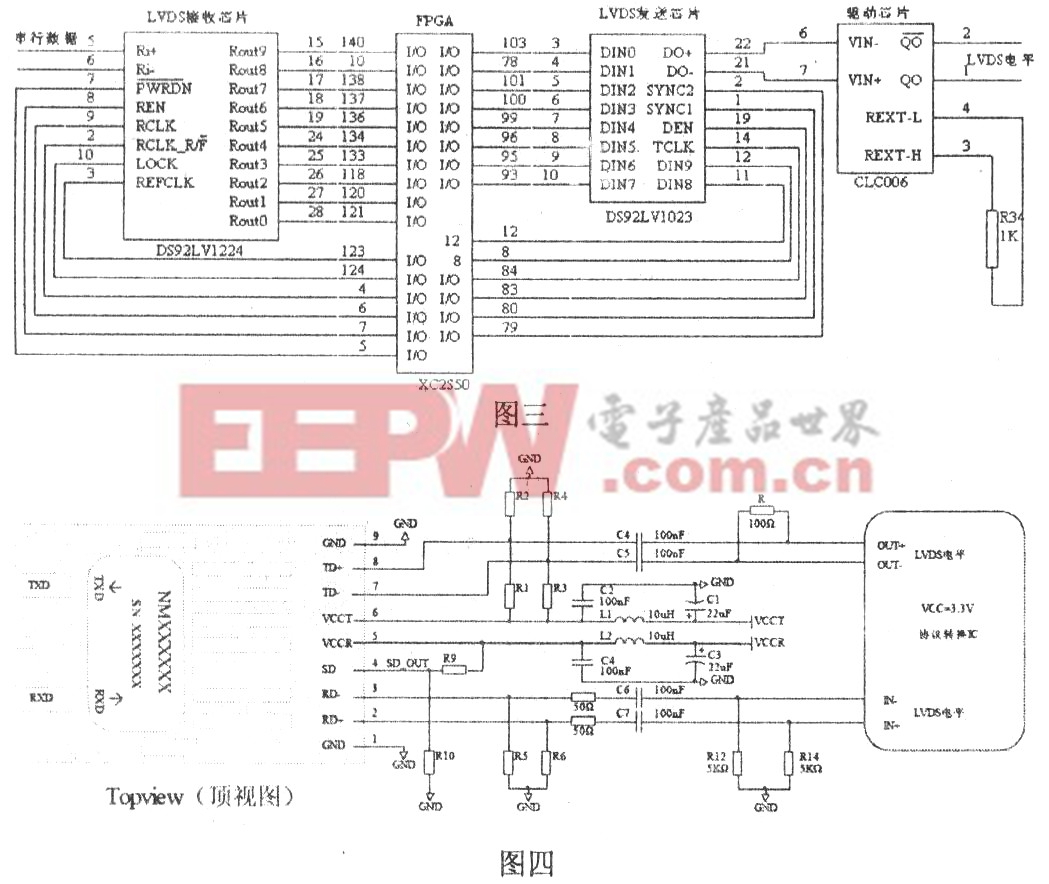

接收端:其部分電路如圖三,解串器DS92LV1224解串出來的數據先經由FPGA模塊再送給LVDS發送芯片,再經過驅動芯片CLC006之后信號變得很強,足以使光模塊接收到此信號。

(2)地面上延長距離設計:

如下圖四,將圖三的LVDS電平直接接到下電路的光模塊的發送端,經過反復試驗,已經可以傳輸10km的距離。在光模塊的接收端將光信號轉成LVDS電平,再經過LVDS模塊轉化成數字信號,再做進一步處理。

4 速度匹配

由于LVDS所傳輸的信號是數據采集系統剛采集到的數據,這個數據的速度只有幾百KByte/s,而這一款LVDS芯片傳輸速度范圍是10一66MByte/s。可以采用間歇式傳輸,但是這種LVDS芯片在傳輸過程中進行中斷后,再次傳輸需要500μs的同步時間,所以如果LVDS芯片進行間歇式傳輸時,會丟失掉500μs的數據,不能采用這種方式。

串行器DS92LV1023和解串器DS92LV1224的芯片有10個數據管腳,一般數據都是8位,其中有兩位一般不用。在這里這兩位空數據位就起到作用了:先將采集回來的數據暫存到FPGA中的內部Fifo里,等到Fif0中數據達到10個字節以上就通知FPGA模塊將數據和時鐘賦到串行器DS92LV1023的管腳上傳輸數據,同時通過FPGA給串行器DS92LV1023的第Data8位賦值為“0”;當傳完采集回來的數據后,我們可以加一些我們自己產生的數據,使LVDS可以持續的傳輸下去,與此同時通過FPGA將串行器DS92LV1023的第Data8位賦值為“1”。

以上是數據源發送端速度配合的處理,下面再談談數據接收端到上傳到計算機上的速度配合。

USB模塊給計算機上傳數據也是間歇式傳輸,也就是說USB模塊每傳512個字節,就要停頓幾個μs。所以就在FPGA中做一個內部Fifo先將數據暫存到內部Fifo里,等到Fifo中數據達到512個字節以上就通知USB模塊可以讀數了,這樣就將數據讀回到計算機里。

通過FPGA控制解串器DS92LV1224PWRDN、REN、RCLK、RCLK_R/F、及REFCLK管腳使LVDS芯片開始解串,由于解串器DS92LV1224解串出來的數據分了兩部分:一是采集的真正數據,二是我們自己加的數據。所以,要先把自己加的數據過濾掉,這個工作讓FPGA來做就可以了,通過FPGA判斷DS92LV1224的Data8位,如果Data8為“0”,則將數據存到FPGA的fifo里。

5 結論

本文介紹了一種基于LVDS總線與光纖結合的高速數據傳輸系統的設計方法,并對設計中整個數據流程、FPGA對LVDS芯片工作狀態和FPGA與單片機的配合作了詳細描述。本系統已經投入實際應用,其性能可靠、穩定,適用性強,該方法值得推廣。

評論