基于低噪音單芯片高頻分頻器的PLL設計

13.5GHz分頻器上市后,設計者可使用低成本的標準元件來構建PLL,從而提供VSAT和其它RF器件所需的高頻率。

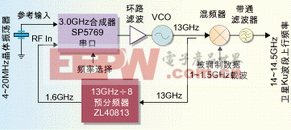

圖4說明了如何使用PLL電路來創建VSAT上行鏈路本地振蕩器。該設計需要一個噪音性能較好的單芯片頻率合成器,如SP5769。這種芯片的最大工作頻率為3GHz,但通過ZL40813 13.5GHz器件將VCO的輸出除以8后(為1.6GHz),可將頻率擴展到13.5GHz。1.6GHz輸入在SP5769中被進一步分頻,然后與晶振參考頻率相比較。SP5769的輸出通過一個充電泵,控制VCO的輸入,構成一個閉合回路。

該電路也可以使用其它單芯片頻率合成器,不過應注意選擇那些能與高頻預分頻器接口的合成器。

在基于BiCMOS技術的合成器中,有些電路的工作速度可能相對較低,因此不能很好地配合高頻分頻器。

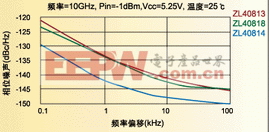

誠然,低相位噪音對VSAT和其它RF器件都十分重要。本例電路中的13.5GHz分頻器是采用互補硅雙極技術構建的,Ft為28GHz。這樣在回路帶寬中產生的噪音與載波的噪音十分接近,不會被PLL消除。

噪音級數與材料的物理特性有關,如GaAs等其它技術本身的噪音級數就比載波噪音要高。圖5列舉了其它13.5GHz分頻器的相位噪音級數。

基于低噪音單芯片高頻分頻器的PLL設計

φn=20log10n

在合成過程中增加的相位噪音可通過如下公式計算:

φn=20log10n

其中,φn是超過相位比較器噪音基底(noise floor)的相位噪音增量,單位為dB;n是合成器的輸出頻率與相位檢測器比較頻率之比。

SP5769中的相位比較器噪音基底為-148dBc/Hz。如果比較頻率為4MHz,而輸出頻率為13GHz,則n為3,250。因此,在回路帶寬中的噪音比相位噪音基底高70dB。假設沒有其它明顯的噪音源,那么13GHz的輸出信號的相位噪音為-78dBc/Hz。

通過類似的方法將頻率從1.6GHz頻分成4MHz,也可以降低分頻器產生的相位噪音,將其產生的噪音降低了52dB,從-140dBc/Hz到-192dBc/Hz。這一數值與比較器的噪音基底相比可忽略不計。采用同樣的辦法將晶振噪音在內部分頻,也可將其忽略不計。

小結

本文描述了如何用新一代的13.5GHz分頻器來擴展低成本商用頻率合成器的頻率范圍,從而降低VSAT等新型高頻應用的成本并推廣其應用。

評論