CAN總線中循環(huán)冗余校驗碼的原理及其電路實現(xiàn)

在CAN系統(tǒng)中為保證報文傳輸?shù)恼_性,需要對通信過程進(jìn)行差錯控制。目前常用的方法是反饋重發(fā),即一旦收到接收端發(fā)出的出錯信息,發(fā)送端便自動重發(fā),此時的差錯控制只需要檢錯功能。常用的檢錯碼兩類:奇偶校驗碼和循環(huán)冗余校驗碼。奇偶校驗碼是一種最常見的檢錯碼,其實現(xiàn)方法簡單,但檢錯能力較差;循環(huán)冗余校驗碼的編碼也很簡單且誤判率低,所以在通信系統(tǒng)中獲得了廣泛的應(yīng)用。下面介紹CAN網(wǎng)絡(luò)中循環(huán)冗余校驗碼(即CRC碼)的原理和實現(xiàn)方法。

1 CRC碼檢錯的工作原理

1 CRC碼檢錯的工作原理

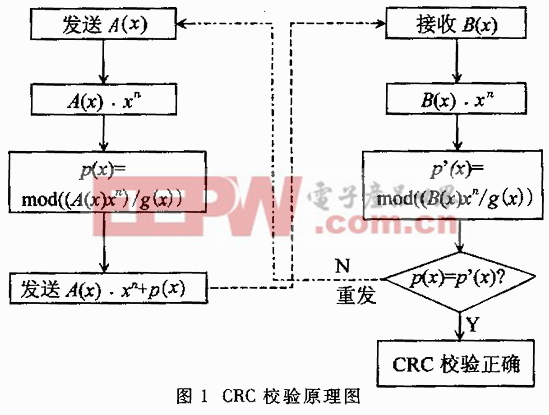

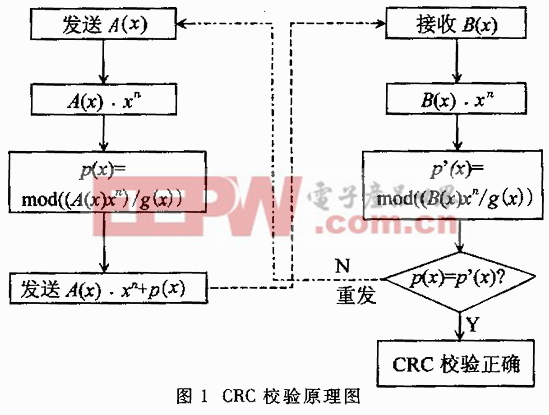

CRC碼檢錯是將被處理報文的比特序列當(dāng)作一個二進(jìn)制多項式A(x)的系數(shù),該系數(shù)除以發(fā)送方和接收方預(yù)先約定好的生成多項式g(x)后,將求得的余數(shù)P(x)作為CRC校驗碼附加到原始的報文上,并一起發(fā)給接收方。接收方用同樣的g(x)去除收到的報文B(x),如果余數(shù)等于p(x),則傳輸無誤(此時A(x)和B(x)相同);否則傳輸過程中出錯,由發(fā)送端重發(fā),重新開始CRC校驗,直到無誤為止。

上述校驗過程中有幾點需注意:①在進(jìn)行CRC計算時,采用二進(jìn)制(模2)運算法,即加法不進(jìn)位,減法不借位,其本質(zhì)就是兩個操作數(shù)進(jìn)行邏輯異或運算;②在進(jìn)行CRC計算前先將發(fā)送報文所表示的多項式A(x)乘以xn,其中n為生成多項式g(x)的最高冪值。對二進(jìn)制乘法來講,A(x)?xn就是將A(x)左移n位,用來存放余數(shù)p(x),所以實際發(fā)送的報文就變?yōu)锳(x)?xn+p(x);③生成多項式g(x)的首位和最后一位的系數(shù)必須為1。

圖1為CRC校驗的工作過程。

目前已經(jīng)有多種生成多項式被列入國際標(biāo)準(zhǔn)中,如:CRC-4、CRC-12、CRC-16、CCITT-16、CRC-32等。CAN總線中采用的生成多項式為g(x)=x15+x14+x10+x8+x7+x4+x3+1??梢钥闯?,CANU叫線中的CRC校驗采用的多項式能夠校驗七級,比一般CRC校驗(CRC-4、CRC-12、CRC-16等)的級數(shù)(二~五級)要高許多,因而它的檢錯能力很強(qiáng),誤判率極低,成為提高數(shù)據(jù)傳輸質(zhì)量的有效檢錯手段。

2 CRC碼的電路實現(xiàn)

2 CRC碼的電路實現(xiàn)

2.1 硬件電路的特點

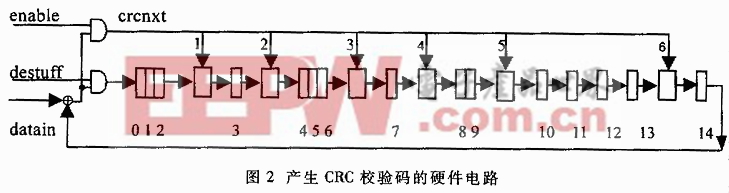

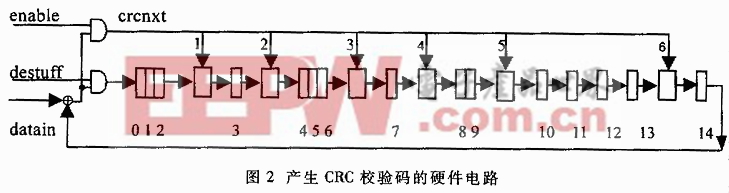

在CAN總線中為了產(chǎn)生CRC碼,硬件電路除了具有復(fù)位和時鐘信號以外,還需要以下兩個控制信號的參與:①填充位解除信號destuff,它的有效邏輯值是1;②CRC檢驗的使能信號enable,有效邏輯也為1。該硬件電路的特點是采用選擇器和反相器代替?zhèn)鹘y(tǒng)設(shè)計中用的異或門,既實現(xiàn)了比較功能,又降低了生產(chǎn)成本,同時也為工程師們提供了一種新的設(shè)計思路。

2.2 硬件電路圖

圖2即為實現(xiàn)CRC碼的硬件電路圖。

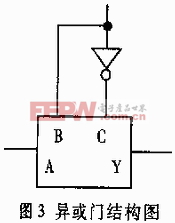

圖中需要說明的幾點如下:①使能信號和填充位解除信號省略;②crcnxt代表的邏輯值為輸入報文序列和CRC寄存器的最高位異或的結(jié)果;③標(biāo)號0~14所指示的為15位CRC寄存器,上升沿觸發(fā);④標(biāo)號1~6所指示的為選擇器和反相器的組合邏輯,實現(xiàn)異或功能,該選擇器的邏輯功能為Y=AB+AC,具體結(jié)構(gòu)如圖3所示。

2.3 電路工作過程

從以上分析可知:①當(dāng)enable=0時,CRC清0;②當(dāng)enable=1、destuff=1時,進(jìn)行正常CRC計算;③當(dāng)enable=1而destuff=0時,正在解除填充時,數(shù)據(jù)暫停傳送。

在各個控制信號均有效時,輸入報文的每一位都是和CRC寄存器的最高位相異和后移入最低位,同時寄存器的第13、9、7、6、3、2位均和其最高位異或,結(jié)果分別左移一位;其它未進(jìn)行異或操作的寄存器位值也分別左移一位,直到報文的每一位都移入CRC寄存器為止,此時寄存器中的值取為計算得到的CRC碼。

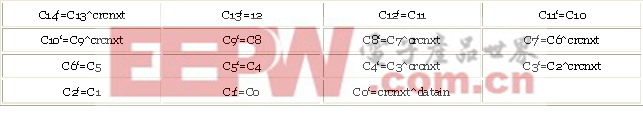

如果報文的比特序列長度為16,則需要左移16次才能對報文的每一位均進(jìn)行處理。如果以Ck表示CRC寄存器的第k位位值、Ck‘表示移位后的第k位位值(k=0,1,2,3……15),則移位規(guī)律見表1。

表1 移位規(guī)律表

表1 移位規(guī)律表

3 CRC校驗碼的軟件實現(xiàn)

CRC校驗用軟件實現(xiàn)起來非常方便。鑒于目前的資料中介紹的方法多使用C語言、匯編語言等實現(xiàn),而缺乏用硬件描述語言實現(xiàn),這里給出CRC碼的Verilog HDL之行為級描述程序。

本程序在Verilog_XL下編譯通過,同時在Synopsis上成功進(jìn)行了綜合及優(yōu)化。

//用Verilog HDL實現(xiàn)CRC碼

module crc(clk,rst,enable,destuff,datain,crc);

input clk;

input rst;

input enable;

input destuff;

input datain;

output[14:0]crc;

reg[14:0]crc;

wire crcnxt=datain^crc[14];

always@(posedge rst or posedge clk)

begin

if(rst)crc=0;

else if(enable destuff)

begin

if(crcnxt)

crc=crc^15h‘4599;

else

crc={crc[13:0],1‘b0};

end

end

endmodule

4 仿真波形

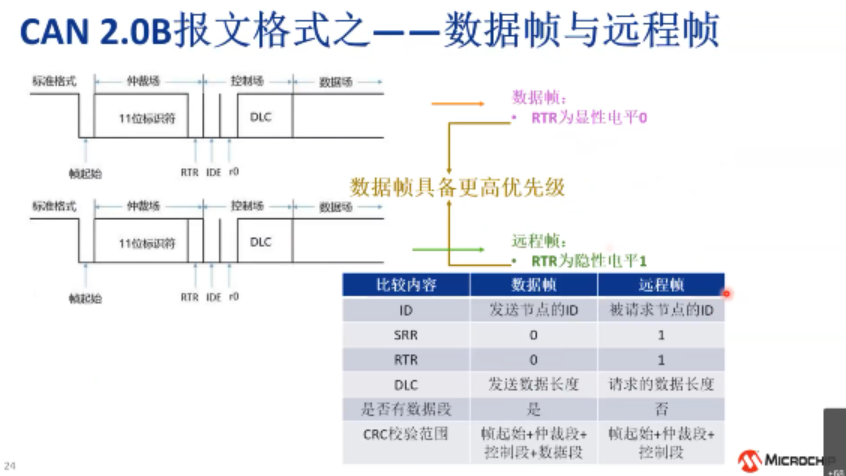

假設(shè)發(fā)送的是一個標(biāo)準(zhǔn)格式的遠(yuǎn)程幀,需求的數(shù)據(jù)字節(jié)為8,標(biāo)識符序列為10101011000,則對上述程序仿真后的波形如圖4所示。Crc序列從第20位開始輸出。

CRC校驗碼的檢錯能力很強(qiáng),并且由于CRC碼檢錯的軟件和硬件實現(xiàn)都很簡單,因而被廣泛地應(yīng)用于各類數(shù)據(jù)校驗中。CRC碼檢錯是提高數(shù)據(jù)傳輸質(zhì)量、高效檢錯的有力手段。

DIY機(jī)械鍵盤相關(guān)社區(qū):機(jī)械鍵盤DIY

評論