基于ECL門電路的UWB信號發(fā)生器的設計

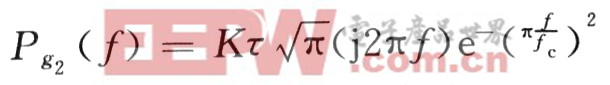

高斯單脈沖(Gaussian Monocycle)即一階高斯脈沖,它是由高斯方程的一階倒數(shù)得出的,其時域表達式為:本文引用地址:http://www.104case.com/article/157775.htm

與上式對應的頻域表達式為:

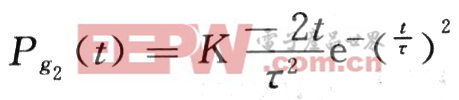

由高斯單脈沖的頻域波形可知,該信號波形含有的直流和低頻分量很小,適合在無線信道中傳輸,且中心頻率隨脈沖寬度變窄而升高,帶寬也隨之增加。

1.2 信號發(fā)生器的方案研究

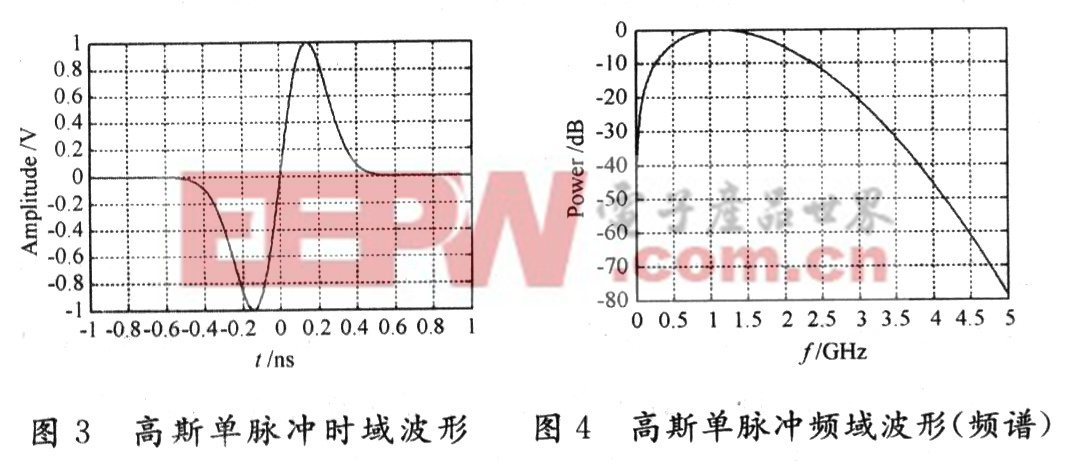

基于1.1節(jié)的分析,信號發(fā)生器的最終輸出信號形式應為高斯單脈沖。為實現(xiàn)該信號,UWB信號發(fā)生器設計成數(shù)字模擬混合電路。ECL門電路是半導體器件中速度最快的開關電路,也是整個電路的核心,它的主要作用是產(chǎn)生脈沖寬度極窄的高斯脈沖,但ECL門電路直接輸出的信號不適于信道傳輸,因而在其后接上模擬電路,以對ECL門電路的輸出信號進行變換,從而獲得UWB通信所需要的高斯單脈沖。圖5是UWB信號發(fā)生器的邏輯原理框圖。

該原理框圖由標準時鐘、電平轉(zhuǎn)換電路、延時器、延時控制電路、ECL門電路、發(fā)送濾波器和脈沖功率放大電路組成。標準時鐘產(chǎn)生器產(chǎn)生一定重復周期的矩形脈沖序列。電平轉(zhuǎn)換電路把時鐘的TTL電平轉(zhuǎn)換成ECL電平。為了精確延時,延時器采用ECL電平的延時芯片,控制電路控制延時芯片的遲延時間,使兩路信號的延時有一個極短的時間差,這樣有時間差的兩路信號通過ECL門電路之后便可產(chǎn)生一個寬度與時間差相等的極窄脈沖。ECL門電路是ECL電平的異或門或者與門,它們的反應速度要足夠快,通常要求其反應時間不能大于250 ps,且外圍電路和傳輸線都應滿足最佳匹配的要求,否則難以得到寬度極窄的理想脈沖。由于ECL門電路的輸入信號都是矩形脈沖,因而通過ECL門電路產(chǎn)生的窄脈沖也是矩形脈沖,又因為輸出脈沖的低電平為3.2 V,該脈沖必定含有豐富的直流和低頻分量,不適于無線傳輸。為了有效傳輸信號,通過發(fā)送濾波器對脈沖形式進行變換,變成需要的高斯單脈沖。由于ECL高低電平的最大差值不過800 mV,通過ECL門電路得來的脈沖功率很小,如果要擴大傳輸距離,則需增大發(fā)射功率,這時把已經(jīng)成形了的高斯單脈沖通過放大電路即可增大發(fā)射功率。

1.3 信號發(fā)生器的電路設計

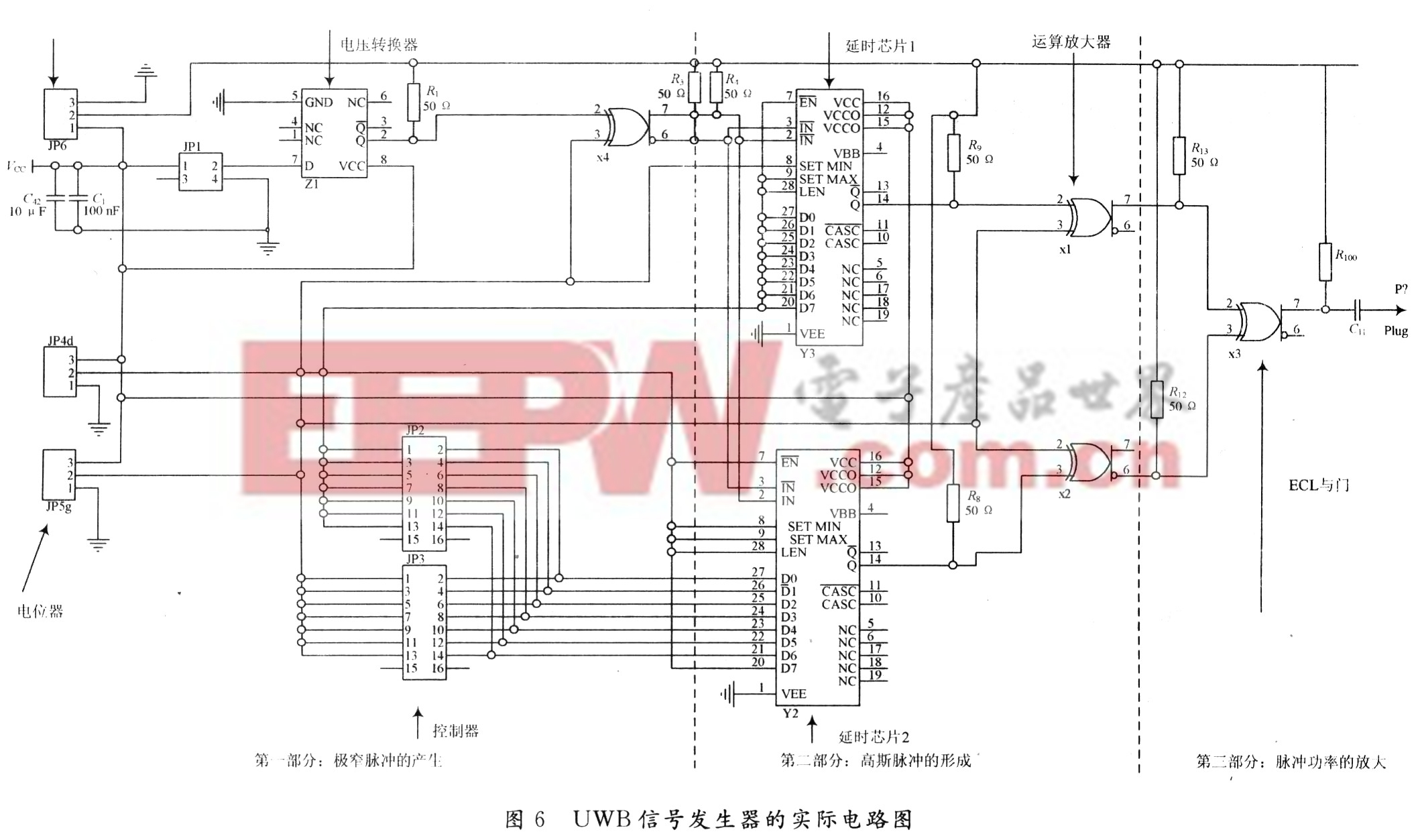

UWB信號發(fā)生器的實際電路完全按照1.2節(jié)中的方案設計。即整體電路主要分為3大部分。第一部分主要功能是產(chǎn)生極窄脈沖。該部分電路對制作PCB板的要求很高,ECL門電路的兩路輸入信號要盡可能對稱,才會最大程度地減少誤差,也即輸出的脈沖寬度才會接近兩路信號的理論延時差。此外,ECL門電路對輸出阻抗有特殊要求,都是50 Ω的特殊阻抗,因而在設計傳輸線時要用微帶線理論去設計,以保證輸出特性阻抗是50 Ω,這樣才不會出現(xiàn)波形較大的失真。

第二部分主要是對第一部分輸出的脈沖進行成形濾波。該部分需要注意的是,運算放大器的速度要足夠快,才能對極窄脈沖進行較好的成形,同時相應的匹配電路要盡可能精確,此外傳輸線都采用微帶線,以保持輸入輸出阻抗匹配,這里的輸入輸出阻抗都是標準的50 Ω。

第三部分是對成形后的高斯單脈沖進行放大。該部分的核心是MMIC(單片微波集成電路),放大電路是可調(diào)的,通過改變VCC達到改變放大電流的目的,傳輸線也都采用微帶線,特性阻抗設計成50 Ω,目的是要和第二部分的輸出阻抗以及發(fā)射天線的特性阻抗匹配,最大限度地提高發(fā)射效率。圖6是UWB信號發(fā)生器的實際電路圖。

DIY機械鍵盤相關社區(qū):機械鍵盤DIY

評論