基于LVDS接口的PC M解碼板設計

3 PCM碼解調設計

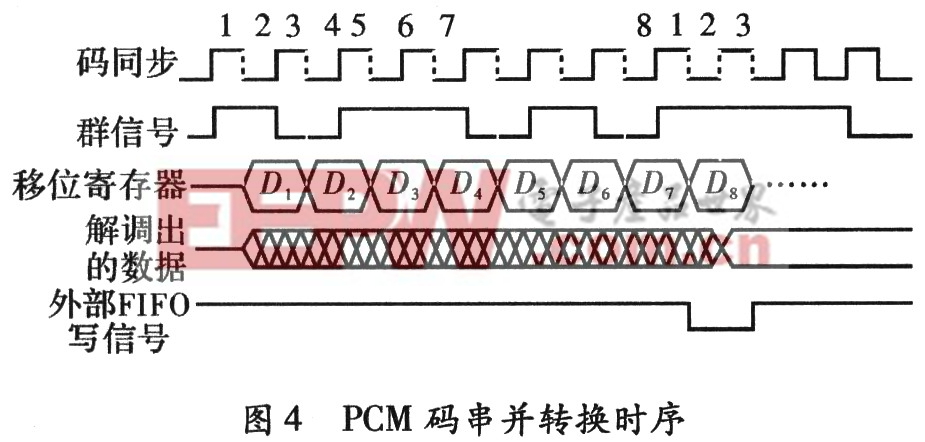

PCM解碼部分用于接收數字量變換器輸出的PCM串行數據并將數據串并轉換。該部分需產生兩種勤務信號,幀同步信號:周期為25 ms,碼寬8μs;碼同步信號:頻率81.92 kHz,占空比50%,用于數字量變換器內部的時序控制。每8個一組的碼同步信號稱作一路,在每幀中從第1路開始排到128路結束。模塊接收的群信號是串行“0”“1”碼,為不歸零碼。PCM解碼部分工作原理:根據幀、碼同步信號時序特征,FPGA生成一個數據時序進程,在時鐘信號的推動下通過地址推進來輸出幀、碼勤務信號。數字量變換器輸出的串行PCM數據流在碼同步信號作用下,通過移位寄存器轉換為8位并行數據,通過寫信號WR同步將解得的并行PCM碼寫入到FIFO中。串并轉換的工作時序,如圖4所示。本文引用地址:http://www.104case.com/article/157728.htm

經多次測試,上位機讀回的數據按照副幀結束標志EB 90兩個bit和幀結束標志14 6F兩個bit所組成數據格式的結果與設計要求吻合。

4 結束語

實踐表明:由于采用低壓差分信號傳送數據,不易受共模噪音影響,可以實現更快的數據傳輸,同時具有低功耗、低噪聲等優良特性;由于總線結構物理層可以采用專用接口芯片實現,而數據鏈路層和傳輸層均可采用可編程邏輯器件FPGA實現。因此,總線硬件實現簡單,易于低成本解決系統高速通信問題。通過測試分析,該板在PCM解碼的抗干擾能力及實現解碼數據的高速、可靠傳輸方面均達到了系統提出的技術指標。

評論