串行 RapidIO: 高性能嵌入式互連技術

摘要

本文引用地址:http://www.104case.com/article/157632.htm 串行RapidIO針對高性能嵌入式系統芯片間和板間互連而設計,它將是未來十幾年中嵌入式系統互連的最佳選擇。

本文比較RapidIO和傳統互連技術的優點;介紹RapidIO協議架構,包格式,互連拓撲結構以及串行RapidIO物理層規范。介紹串行RapidIO在無線基礎設施方面的應用。

RapidIO 與傳統嵌入互連方式的比較

隨著高性能嵌入式系統的不斷發展,芯片間及板間互連對帶寬、成本、靈活性及可靠性的要求越來越高,傳統的互連方式,如處理器總線、PCI總線和以太網,都難以滿足新的需求 。

處理器總線主要用作外部存儲器接口,如德州儀器(TI) C6000系列DSP的外部存儲器接口,可支持外接同步SDRAM、SBSRAM及FIFO,也可支持異步SRAM、FLASH等。外部存儲器接口也可用作與板內FPGA或ASIC芯片互連,這種情況下,FPGA或ASIC模擬一個DSP支持的存儲器接口,DSP則把FPGA或ASIC當作存儲器來訪問。這類同步接口帶寬可達10Gbps,如德州儀器TMS320C6455 DSP的DDR2接口最大帶寬為17.066Gbps,SBSRAM接口最大帶寬為8.533Gbps。然而,這種接口也存在一些局限性:

1. 接口管腳多,硬件設計困難。常見的DDR2接口有70~80個管腳;

2. 只能用于板內互連,無法用于板間互連;

3. 不是點對點的對等互連,DSP始終是主設備,其它器件只能做從設備。

PCI是廣泛用于計算機內器件互連的技術。傳統PCI技術也采樣類似于上述存儲器接口的并行總線方式,如TMS320C6455 DSP的PCI接口,有32bits數據總線,最高時鐘速度為66MHz,共有42個管腳。最新的串行PCI Express技術采用與串行RapidIO(SRIO, Serial RapidIO)類似的物理層傳輸技術,使得帶寬達到10Gbps左右。但由于其主要的應用仍是計算機,而且為了兼容傳統PCI技術,使得它在嵌入式設備方面的應用具有一定的局限性,如不支持點對點對等通信等。

眾所周知,以太網是使用最廣泛的局域網互連技術,它也被擴展應用到嵌入式設備互連,但它的局限性也是顯而易見的:

1. 不支持硬件糾錯,軟件協議棧開銷較大;

2. 打包效率低,有效傳輸帶寬因此而減小;

3. 只支持消息傳輸模式,不支持對對端設備的直接存儲器訪問(DMA, Direct Memory Access)。

針對嵌入式系統的需求以及傳統互連方式的局限性,RapidIO標準按如下目標被制定:

1. 針對嵌入式系統機框內高速互連應用而設計。

2. 簡化協議及流控機制,限制軟件復雜度,使得糾錯重傳機制乃至整個協議棧易于用硬件實現。

3. 提高打包效率,減小傳輸時延。

4. 減少管腳,降低成本。

5. 簡化交換芯片的實現,避免交換芯片中的包類型解析。

6. 分層協議結構,支持多種傳輸模式,支持多種物理層技術,靈活且易于擴展。

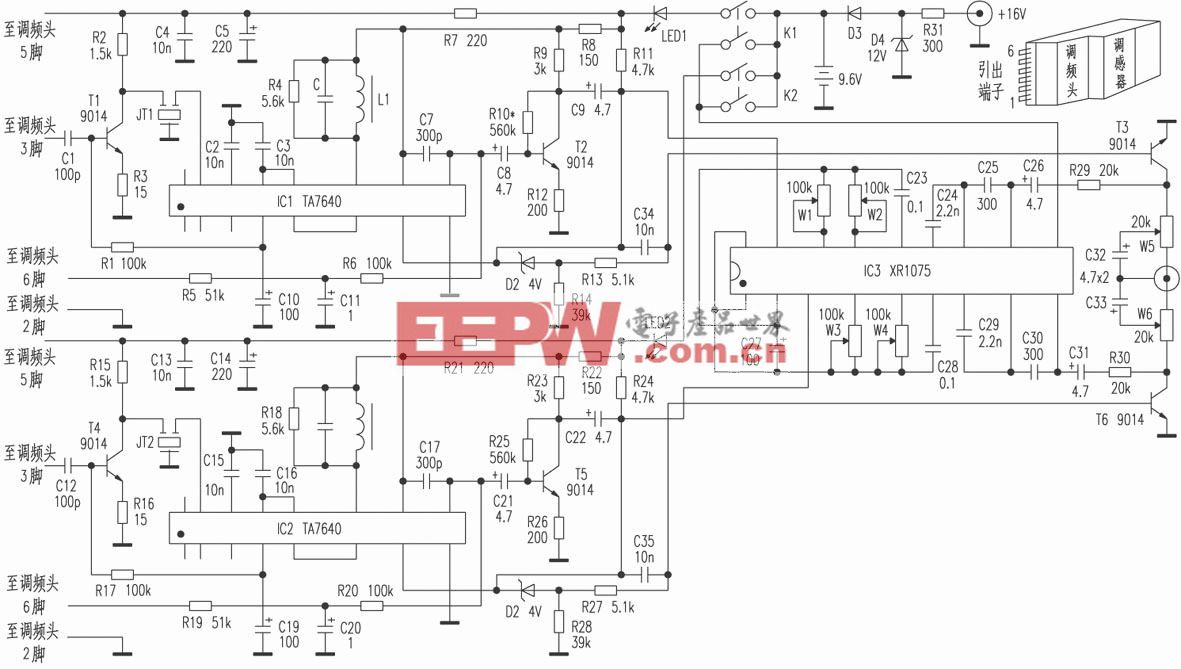

圖1展示了RapidIO互連在嵌入式系統中的應用。

圖1 RapidIO在嵌入式系統中的應用

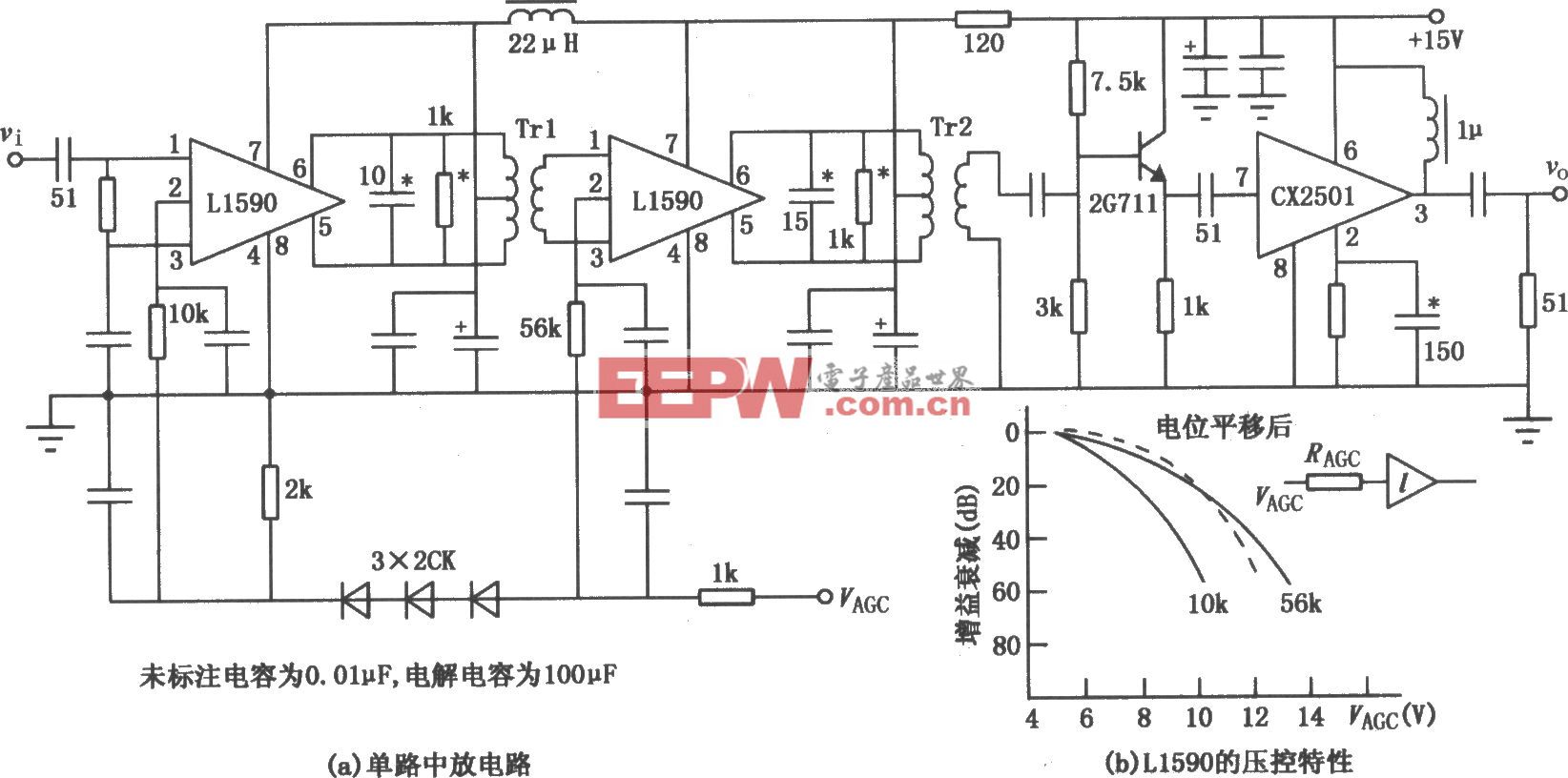

表1總結比較了的三種帶寬能達到10Gbps的互連技術:以太網,PCI Express和串行RapidIO,從中可以看出串行RapidIO是最適合高性能嵌入式系統互連的技術。

表1 10G級互連技術比較

軟件實現TCP/IP 協議棧的以太網 4x PCI Express 4x SRIO 備注

軟件開銷 高 中 低 SRIO 協議棧簡單,一般都由硬件實現,軟件開銷很小

硬件糾錯重傳 不支持 支持 支持

傳輸模式 消息 DMA DMA,消息

拓撲結構 任意 PCI樹 任意 SRIO支持直接點對點或通過交換器件實現的各種拓撲結構

直接點對點對等互連 支持 不支持 支持 SRIO互連雙方可對等的發起傳輸。

傳輸距離 長 中 中 SRIO針對嵌入式設備內部互連,傳輸距離一般小于1米

數據包最大有效載荷長度 1500字節 4096字節 256字節 嵌入式通信系統對實時性要求高,SRIO小包傳輸可減少傳輸時延

打包效率 (以傳輸256字節數據為例) 79% (TCP包) 82% 92~94% 打包效率是有效載荷長度與總包長的比率。SRIO支持多種高效包格式。

串行RapidIO協議

RapidIO行業協會成立于2000年,其宗旨是為嵌入式系統開發可靠的,高性能,基于包交換的互連技術。RapidIO協議的簡要發展歷史是:

1. 2001年初,最初的標準被發布

2. 2002年6月,1.2版標準發布

3. 2005年6月,1.3版標注發布

串行RapidIO是物理層采用串行差分模擬信號傳輸的RapidIO標準。SRIO 1.x 標準支持的信號速度為1.25GHz、2.5GHz、3.125GHz;正在制定的RapidIO 2.0標準將支持5GHz、6.25GHz.

目前,幾乎所有的嵌入式系統芯片及設備供應商都加入了RapidIO行業協會。德州儀器(TI) 2001年加入該組織,2003年成為領導委員會成員。2005年底,德州儀器(TI)推出第一個集成SRIO(Serial RapidIO)的DSP,后來又陸續推出共5款支持SRIO的DSP,這使得RapidIO的應用全面啟動。

RapidIO協議結構及包格式

評論