高速串行總線技術(shù)發(fā)展與應(yīng)用分析

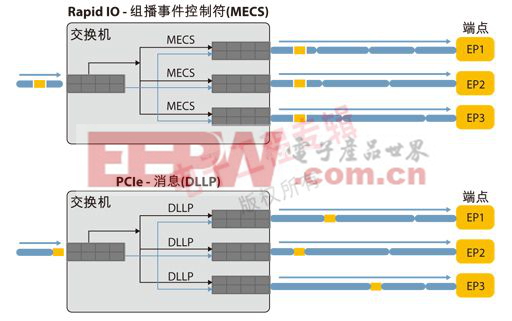

除了更有效的流量控制外,將控制符嵌入進(jìn)數(shù)據(jù)包使得RapidIO具有PCIe和以太網(wǎng)目前無法提供的能力。控制符可以用來低時延和低抖動地在整個RapidIO系統(tǒng)中分配事件,如圖2所示。

圖2:RapidIO組播事件控制符和PCIe DLLP。

這一功能可以支持將公共實(shí)時時鐘信號分配到多個端點(diǎn)或?yàn)樘炀€系統(tǒng)分配幀信號等應(yīng)用,還可以用于發(fā)送其它系統(tǒng)事件信息,以及實(shí)現(xiàn)多處理器系統(tǒng)中的調(diào)試。如圖2 所示,PCIe的DLLP在每次通過交換機(jī)傳送時都會引入很大的時延和抖動。相反,RapidIO協(xié)議允許在整個RapidIO架構(gòu)中分配信號時具有低于 10個單位間隔(UI)的抖動性能和每次交換低于50ns的時延性能,并且與數(shù)據(jù)包業(yè)務(wù)無關(guān)。

PCIe和以太網(wǎng)可以選擇擴(kuò)展各自的規(guī)范以允許事件獲得低時延的分配。引入類似控制符的概念對以太網(wǎng)來說是很大的進(jìn)步。以太網(wǎng)生態(tài)系統(tǒng)下已有幾家組織正在改進(jìn)存儲應(yīng)用中的以太網(wǎng)能力,其中就可能需要用到類似控制符的概念。以太網(wǎng)還準(zhǔn)備采用簡單的XON/XOFF流量控制來進(jìn)一步增強(qiáng)性能。

PCIe目前不允許將DLLP嵌入進(jìn)TLP,因?yàn)檫@一概念不能兼容傳統(tǒng)的PCI/X總線操作。嵌入TLP的DLLP會產(chǎn)生沒有數(shù)據(jù)可以放置到傳統(tǒng)總線上的周期。PCIe端點(diǎn)可以工作在存儲-轉(zhuǎn)發(fā)模式,確保數(shù)據(jù)包在轉(zhuǎn)發(fā)給總線之前全部接收到,代價(jià)是時延的顯著增加和吞吐量的降低。由于PCIe主要用于單處理器系統(tǒng)的板上互連,并且一直需要保持與傳統(tǒng)總線標(biāo)準(zhǔn)的兼容,PCIe陣營不太可能允許DLLP被嵌入進(jìn)TLP。

帶寬選項(xiàng)

除了流量控制和鏈路維護(hù)外,以太網(wǎng)、PCIe和RapidIO在物理/鏈路層方面的最顯著區(qū)別是所能支持的帶寬選項(xiàng)。以太網(wǎng)帶寬具有一代增加10倍的悠久歷史。以太網(wǎng)目前工作在 10Mbps、100Mbps、1Gbps和10Gbps。一些專用器件甚至支持2Gbps(2.5GBaud)。下一代以太網(wǎng)將能工作在40Gbps和 /或100Gbps。

PCIe和RapidIO采用了不同的方法,因?yàn)榘迳稀彘g和設(shè)備間互連要求功率與數(shù)據(jù)流匹配。因此與以太網(wǎng)相比, PCIe和RapidIO支持更多的通道速率和通道帶寬組合。PCIe 2.0允許通道工作在2Gbps或4Gbps(2.5和5Gbaud),而RapidIO支持1、2、2.5、4和5Gbps(1.25、2.5、 3.125、5和6.25Gbaud)的通道速率。PCIe和RapidIO都支持從單個通道到16個通道的通道帶寬組合。PCIe規(guī)范中還支持32通道端口。對于給定的通道帶寬,RapidIO端口可以提供多于或少于PCIe的帶寬,因此允許系統(tǒng)設(shè)計(jì)人員調(diào)整系統(tǒng)中用于數(shù)據(jù)流的功率大小。

傳輸層

RapidIO和以太網(wǎng)標(biāo)準(zhǔn)都是模糊拓?fù)浣Y(jié)構(gòu)。任何端點(diǎn)組都可以用任何拓?fù)浣Y(jié)構(gòu)連接,包括環(huán)形、樹形、網(wǎng)狀、超立方體以及超復(fù)雜網(wǎng)絡(luò)等更深奧的幾何圖形。數(shù)據(jù)包則根據(jù)它們的網(wǎng)絡(luò)地址在這些拓?fù)渲型瓿陕酚伞;ヂ?lián)網(wǎng)協(xié)議(IP)地址就是一種以太網(wǎng)網(wǎng)絡(luò)地址。 RapidIO網(wǎng)絡(luò)地址被稱為目的識別符,簡稱destID。

與拓?fù)錈o關(guān)的(Topology-agnostic)協(xié)議可實(shí)現(xiàn)各種資源備份和冗余功能。例如,一些系統(tǒng)使用N+1備份策略來確保高可用性和可靠性,而不用顯著增加硬件數(shù)量。(備份功能將未使用的設(shè)備作為在用設(shè)備的備份。在N+1 備份機(jī)制時,N個元件有一個共同的備份,因此當(dāng)N個元件中的一個發(fā)生故障時系統(tǒng)可以繼續(xù)工作。這個策略也被稱為1:N備份)。支持不同拓?fù)溥x項(xiàng)還允許系統(tǒng)設(shè)計(jì)人員通過匹配數(shù)據(jù)路徑和數(shù)據(jù)流程消除系統(tǒng)中的性能瓶頸。系統(tǒng)擴(kuò)展和演變在RapidIO和以太網(wǎng)絡(luò)中是不受約束的。

相反,PCIe在頂層支持帶單個根聯(lián)合體(Root Complex)的樹狀結(jié)構(gòu)。PCIe還使用了多種路由算法,具體取決于TLP類型。PCIe支持的單路拓?fù)涫莻鹘y(tǒng)PCI/X總線支持的一部分。PCIe 標(biāo)準(zhǔn)已經(jīng)用多根I/O虛擬化(MRIOV)進(jìn)行了擴(kuò)展,進(jìn)一步增加了PCIe可以支持的物理拓?fù)鋽?shù)量。然而,由于MRIOV實(shí)現(xiàn)代價(jià)高,是否能被PCIe 生態(tài)系統(tǒng)采納還是未知數(shù)。PCIe元件還支持非透明橋接(NTB)功能,因此一個PCIe層可以訪問另一個PCIe層中的確定存儲范圍。這種方法的系統(tǒng)可靠性和可用性將在后文作進(jìn)一步闡述。

許多基于以太網(wǎng)的系統(tǒng)功能也受限于樹形結(jié)構(gòu)。例如,許多以太網(wǎng)實(shí)現(xiàn)使用不同生成樹協(xié)議(STP)將可用鏈路組減少到樹形使用鏈路。作為將以太網(wǎng)擴(kuò)展到存儲網(wǎng)絡(luò)的一部分努力,協(xié)議中規(guī)定可以為以太網(wǎng)支持的4096個虛擬通道中的每個通道創(chuàng)建生成樹,這樣可以允許同時使用更多的鏈路。然而,支持4096個虛擬通道會增加交換的復(fù)雜性,可能需要更多的緩存,并增加通過交換機(jī)的時延。

邏輯層

RapidIO、PCIe和以太網(wǎng)在邏輯層方面也有多個差異較大的地方。最明顯的區(qū)別是所支持的語義

評論