超短波頻段脈沖產生器的設計及硬件實現

2 具體電路實現

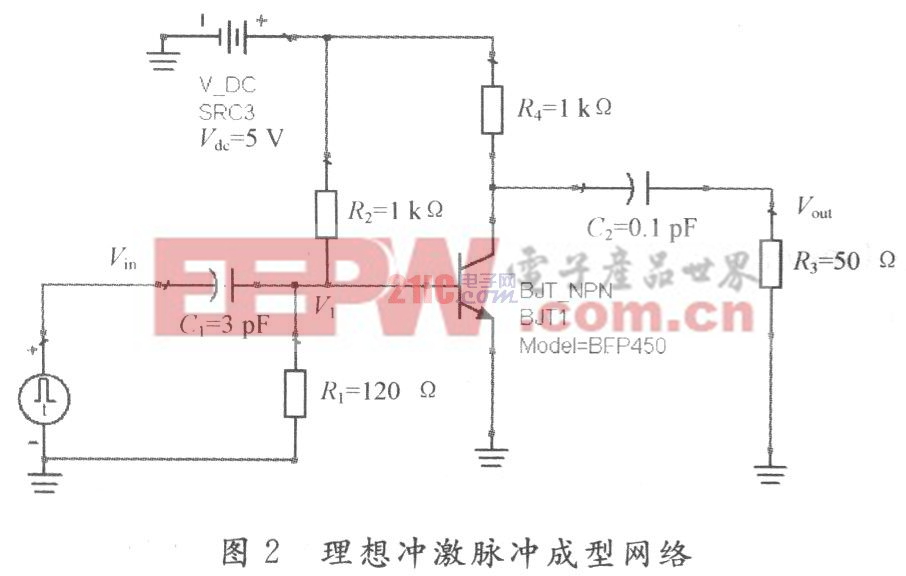

利用Agilent的ADS2006A對電路進行仿真設計,理想沖激脈沖發生器由激勵信號源,微分網絡,零偏置放大電路組成,如圖2所示。

激勵信號源為TTL電平的方波信號Vin,上升沿和下降沿均為1 ns,激勵信號寬度為400 ns。微分網絡由RC時間常數比輸入脈沖持續時間少很多的高通電路組成。這種電路用來將加于輸入端的方波電壓變為正負的尖峰電壓輸出。因為輸出電壓表示了輸入電壓的變化率,所以這個變化過程叫作微分。微分電路設計的兩個重點:τ<<t外加/10,以獲得良好的沖激響應;對電阻R進行合理的取值以獲得足夠大的電壓幅度。在此設計中,C1=3 pF,R=120 Ω,時間常數τ=RC=3×10-12×120=3.6 ns。

零偏置放大網絡采用單級晶體管共射放大電路,BJT采用的是infineon公司的BFP450,因為要使放大電路濾去負脈沖,所以必須使晶體管工作在截止區和放大區的臨界點。設計單級晶體管放大電路的步驟是先靜態,后動態。通過ADS對BFP450進行直流工作點測試,找到合適的靜態工作點。在零偏置放大電路中,R2和微分電路中的R1共同構成了分壓式直流通路。

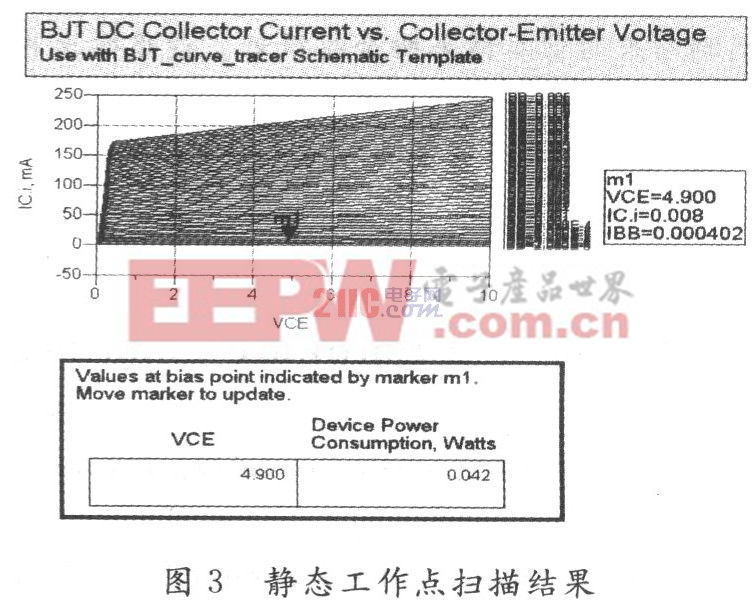

根據BFP450的datasheet得知最大基極電流IBB=10 mA,最大集電結電壓為VCE=15 V,所以掃描范圍為:IBB=20~100μA,步進為10μA。VCE=0~10 V,步進為O.1 V。將BFP450的Spice模型導入ADS中,得到靜態工作點掃描結果,如圖3所示。

從掃描結果中可以看出,對于IBB20μA,都可以認為晶體管進入了截止區。同時在設置靜態工作點時,盡量使電路有一個較大范圍的線性放大區,這樣更有利于脈沖的放大。所以選取的試驗條件為:VCE=4~5V,步進0.1V。VCE=500~600mV,步進20mV。在此范圍內,根據公式:

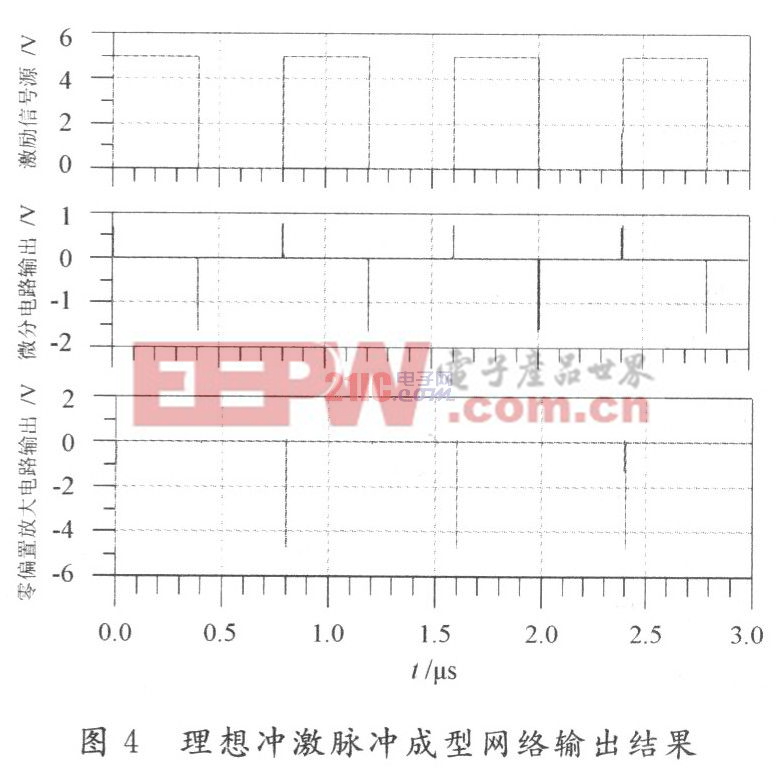

推導出R2=1 kΩ,R4=1 kΩ。再將阻值帶回偏置電路中,得到靜態工作點為IBB=14.96 μA,Ic=23.77μA,VBE=534.1 mV,VCE=4.976 V。理想沖激脈沖成型網絡的各級輸出如圖4所示。

從輸出結果來看,基本達到了預期結果,提取出了正向微分信號,并倒相放大到5 V,拖尾振蕩很小。

評論