基于IEEE 1588的時鐘同步技術在分布式系統中的應用

5 基于FPGA的硬件同步方案

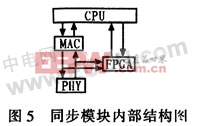

因為采用硬件電路獲取時間戳,從而獲得更高的同步精度,這里采用FPGA實現時間戳的獲取和從時鐘相對主時鐘的頻率糾偏。分布式系統中節點時鐘同步模塊的內部結構如圖5所示。

每個節點包含CPU、以太網媒體訪問控制器(MAC)、以太網物理層收發器(PHY)、FPGA等4種主要器件。物理層收發器和MAC控制器通過標準的MII接口相連,CPU通過總線與MAC控制器和FPGA相連。物理層收發器、MAC控制器和CPU構成通訊協議棧完成數據包的發送和接收。

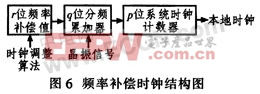

為了使從時鐘的晶振頻率與主時鐘保持一致,FPGA中需要有一個頻率可調的時鐘以實現晶振糾偏,如圖6所示,由r位頻率補償值寄存器、g位分頻累加器、p位系統時鐘計數器組成,一個普通晶體振蕩信號輸入FPGA模塊。在每個晶振周期,r位頻率補償值寄存器內保存的頻率補償值累加到q位分頻累加器中,與累加器中的值相加。

如果發生溢出,則在下一個晶振周期,時鐘計數器增加一個增量,這個增量就是整個頻率補償時鐘的分辨率;如果沒有溢出,則在下一個晶振周期,時鐘計數器保持原值。計數器的當前值即為調整后的本地時鐘。因此可以通過改變頻率補償值來改變時鐘計數器數值增加的頻率,實現對晶振頻率的補償。q和r越大,頻率補償值的改變對累加器發生溢出的頻率的影響越小,對晶振頻率的補償越精細。本系統選擇r=32,q=32,p=64。

使用FPGA不但能夠獲得最精確的時間戳,而且能夠采用數字電路的方法精確補償從時鐘的晶振頻率。FPGA的控制器實現時鐘調節算法,并由得到的時間戳和本地時鐘相比較,得到頻率補償值,從而控制時鐘計數器數值,補償晶振的頻率。而CPU則主要負責驅動MAC控制器完成相關的通訊功能。

6結束語

采用IEEE 1588精確時鐘同步協議的以太網時鐘同步技術,解決了通用以太網實時性和同步性差的問題。為基于多播技術的標準以太網的實時應用提供了有效的解決方案。IEEE 1588精確時鐘同步協議的制定滿足網絡化分布式系統的需求,利用IEEE 1588時鐘同步技術可以在不增加網絡負荷的情況下,實現整個分布式系統的高精度時鐘同步,從而可以有效解決分布式系統的實時性問題,進而改善和提高系統的同步精度。

評論