基于CY7C68013的高速數據傳輸系統的設計

摘 要: 采用Cypress公司的CY7C68013芯片設計了通用的USB接口,結合MAX7128的串/并/串轉換和光纖收發系統,實現數據的高速傳輸。介紹了系統的軟硬件結構, 詳細介紹了固件設計和WDM驅動程序的結構、特性、工作機制、軟件流程及與USB設備通信的方法。測試表明,該系統達到了預期的設計目標和實用要求。

本文引用地址:http://www.104case.com/article/157107.htmUSB控制器是以USB串口引擎為主的專用集成電路,并可延伸至對其進行管理的MCU以及相應的軟硬件。目前市場上供應的USB控制器主要有2種:帶USB接口的單片機(MCU)或純粹的USB接口芯片。帶USB接口的單片機可分為2類:一類是從底層設計專用于USB控制的單片機,如Cypress公司的CY7C63513、CY7C64013等[1],由于開發工具的專用性,往往應用于各種專業應用場合,如微機主板等[2-4];另一類是增加了USB接口的普通單片機,如Intel公司的8X931、8X930以及Cypress公司的EZ-USB,由于均基于8051內核,因而得到了廣泛應用。

1 CY7C68013與系統結構簡介

Cypress公司的CY7C68013芯片是集成USB2.0協議的微處理器,支持12 Mb/s的全速傳輸和480 Mb/s的高速傳輸,具有控制傳輸、中斷傳輸、塊傳輸和同步傳輸4種傳輸方式,內部包括一個增強型8051處理器內核、一個串行接口引擎(SIE)、一個USB收發器、8.5 KB片上RAM和4 KB FIFO存儲器以及一個通用可編程接口(GPIF)。8051可工作在48 MHz/24 MHz/12 MHz時鐘頻率,內部可自動產生480 MHz的頻率供USB2.0串行收發引擎使用。由于數據緩沖器與SIE相連接,數據進入收發器后,通過SIE可直接轉向FIFO,通過8 bit或16 bit數據接口與外設連接,存取數據。微控制器不參與數據傳輸,但允許以FIFO或RAM的方式訪問這些共享FIFO,從而實現低速控制、高速傳輸。CY7C68013有GPIF/SLAVE FIFO/GPIO 3種接口模式,本系統采用Slave FIFO接口模式,選用控制傳輸和塊傳輸2種方式,外部控制器可像普通FIFO一樣對FIFO進行讀寫。

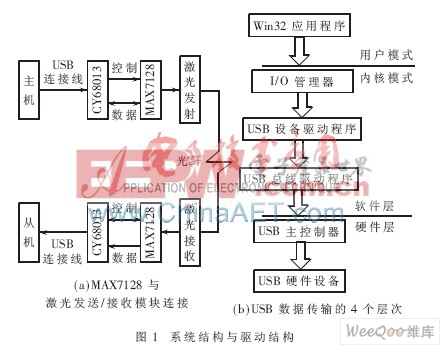

本數據傳輸系統分為3部分:發送端和接收端、CY7C68013控制器、具有并/串(或串并轉換)功能的CPLD芯片(MAX7128)以及光纖傳輸模塊。其中,CY7C68013和MAX7128之間采用并行連接方式,MAX7128與激光發送(接收)模塊間是串行連接,如圖1(a)所示。

圖1(a)中,主機將數據發送到CY7C68013端點FIFO緩沖器中,然后CY7C68013將端點FIFO中的數據分字節放到一組I/O口上,并且使能讀信號,MAX7128讀取I/O上的邏輯值,當接收512 B后,MAX7128將這512 B的數據從低到高串行發送給激光發送模塊;數據經過光纖傳輸,進入激光接收模塊,輸出串行信號,通過MAX7128實現串并轉換,數據寬度為8 bit,通過CY7C68013的從屬FIFO的寫入時序即可將數據寫入CY7C68013的端點緩沖器中。

USB數據傳輸接口開發分為4個層次,接口硬件、接口軟件、驅動和應用程序如圖1(b)所示。

評論