基于軟件無線電的衛星通信模擬源的實現

O 引言

通信中普遍采用基帶信號對載波波形的某些參量(如振幅、頻率以及相位等)進行調制,以滿足系統發射和接收的需要。隨著現代電子技術的飛速發展,器件工藝越來越先進,器件功能越來越強,實現信號調制的方法也越來越多,實現信號調制的穩定度和可靠性都在不斷提高。尤其在衛星通信系統中,信號調制的應用越來越廣泛,要求也不斷提高。采用現代數字信號處理技術實現的調制方法,各種信號的產生依靠軟件操作來確定,同一信號經過數字化后可由不同的軟件模塊來實現各種調制功能。這使得硬件電路結構變得更加簡單,操作更加方便,穩定度更高,可靠性更強。而且結合相應的數字信號處理軟件及控制軟件可以加載新的調制方式,形成一個通用的數字調制器,能夠方便靈活地進行通信調制方式的擴展。

軟件無線電是一種基于寬帶模數/數模轉換器件、高速數字信號處理芯片,以軟件為核心(Software-Oriented)的嶄新的體系結構。軟件無線電技術的發展為衛星通信系統提供了良好的發展基礎。由于FPGA具有高度的靈活性和重配置性,其在基于軟件無線電的通信系統中應用越來越廣泛。該設計是基于軟件無線電,采用FPGA實現全數字調制的通用衛星信號源模塊,數據協議及調制方式任意可變,可以靈活地應用于各種衛星通信系統中。

1 硬件系統設計

軟件無線電技術要求靠近天線的地方盡可能使用寬帶的數模/數模轉換器,盡早地完成信號的數字化,從而使得無線電臺的功能盡可能地用軟件來定義和實現。但是由于受寬帶天線、高速A/D,D/A及DSP等技術水平的限制,實現一個理想的軟件無線電平臺的條件目前還不具備。因此,現在對軟件無線電的研究一方面集中在上述關鍵技術的研究上,另一方面更多地是在現有的技術條件下,研究如何最大程度地實現軟件無線電所要求的通用性和靈活性,將軟件化、通用化的設計思想體現到具體的應用實踐中。雖然目前基于軟件無線電的直接射頻收發系統的實現還有些難度,但基于中頻數字信號處理的中頻收發技術已相當成熟。本衛星通信模擬源就是采用基于軟件無線電的中頻發送技術,以高速DAC和高端FPGA為硬件載體,給出了模擬中頻信號的輸出。系統結構框圖如圖1所示(完整的發送系統還需要混頻器、放大器及天線等,這不在本文的討論范疇內),FPGA對數據進行編碼調制后再送給DAC,以產生中頻輸出。

衛星通信模擬數據源既可由FPGA內部產生,也可以由外部送入。為了保證硬件平臺的通用性,本衛星通信模擬源系統的外部接口有TTL,422及LVDS等類型,用以滿足各種不同的接口需要。FPGA是整個系統的核心器件,為了保證處理速度和邏輯單元的容量,采用Altera公司Str-atixⅡ系列FPGA——EP2S90F1020。EP2S90F1020擁有72 768個寄存器和72 768個算術查找表單元,另有4 Mb存儲器單元和384個9 b乘法器,其工作速度快,資源非常豐富,可以在內部進行絕大部分的數字中頻處理運算。

為了保證中頻輸出信號的質量,DAC的采樣時鐘最好大于等于載波頻率的4倍。如載波中頻為70 MHz,則DAC的采樣時鐘應為280 MHz或更高。再考慮系統的可編程性和升級性,采用了Analog Devices公司的超高速DAC——AD9736。AD9736的數據精度為14 b,采樣率高達1 200 MSPS,采用DDR方式LVDS數據接收器,電流型輸出,內置同步控制電路,適合應用在寬帶通信系統中。

由于硬件系統的工作頻率很高,需要采用高速電路設計方法,需要注意以下幾點:

信號完整性 需要對板級系統進行信號完整性仿真,注意阻抗匹配,減小關鍵信號線之間的串擾,控制數據總線之間的延時;

電源完整性 需要對板級系統進行電源完整性仿真,增加線和過孔上所能通過最大電流的裕量,通過在合適的位置加去耦電容,以降低電源和地平面上的交流阻抗;

電磁兼容 由于硬件屬于模/數混合電路,在布線時需要注意模擬部分和數字部分的隔離,采用獨立的模擬電源和數字電源以及模擬地和數字地,特別要注意降低數字部分對模擬部分的干擾;

功耗問題 隨著系統工作頻率的提高,系統的功耗也隨之增加,需要對關鍵器件進行散熱處理。

2 軟件系統實現

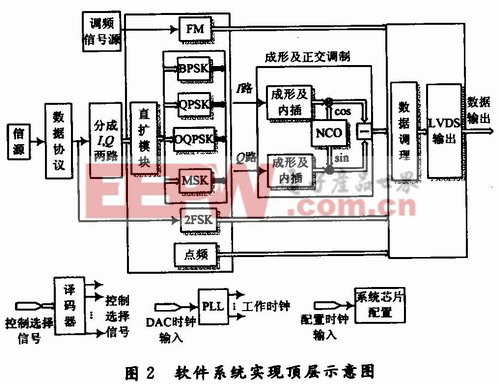

軟件系統主要包括芯片配置、數據協議、基帶數據調制、內插成形濾波以及正交調制等模塊。芯片配置模塊主要對DAC等芯片進行初始化配置,設置其工作方式。數據協議模塊定義了數據打包成幀的結構,協議和調制方式相對應。基帶數據調制模塊包含各種基帶調制方式的實現,如BPSK,QPSK,OQPSK,MSK及BFSK等。內插成形濾波模塊負責對基帶調制后的數據進行內插成形濾波,以滿足系統帶寬和數據率的需要。正交調制模塊主要對I/Q數據進行數字上變頻(DUC)處理。調制方式和數據協議的選擇可通過譯碼器來實現。具體的軟件系統如圖2所示。

評論