AD9779A的寄存器配置及PLL頻帶優化

隨著科學技術的發展,通信、測量等各個領域對信號源的要求越來越高,高速任意波形發生器成為市場的熱點。高速DAC作為任意波形發生器的關鍵部分,其性能對高速信號有著極大的影響。AD9779A是目前國內能買到的性能較高的高速DAC芯片,內部集成PLL倍頻電路、同步控制、增益控制等功能模塊,通過SPI接口和外部通信,可以設置優化各種功能以達到最佳性能。

本文引用地址:http://www.104case.com/article/156608.htm1 AD9779A簡介

AD9779A是Analog Devices公司生產的雙通道16位高速寬動態范圍數DAC,采樣率1Gsps,允許高至奈奎斯特頻率的多載波生成。0.18μm CMOS工藝制作,工作電壓1.8~3.3 V,采樣率1 Gsps時功耗1 W,具有高速、低功耗的特點。AD9779A還包含低噪聲高性能的PLL時鐘倍頻電路,可以減輕板級時鐘輸入的負擔。AD9779A可以應用在無線基礎設施(WCDMA/CDMA2000/TD/GSM)、數字頻率合成、寬帶通信等領域。

2 AD9779A的SPI通信方式

2.1 AD9779A的SPI接口簡介

SPI總線系統是一種同步串行外設接口,它可以使MCU與各種外圍設備以串行方式進行通信,以交換信息。通過AD9779A的SPI接口可以配置內部的寄存器,設置各種功能以達到設計要求。AD9779A的SPI接口支持單字節或多字節傳輸,包括高位優先和低位優先格式,由4根線組成,分別是:

①串行時鐘(SCLK),作為數據輸入輸出的同步時鐘,最大時鐘速率40 MHz。輸入數據在時鐘的上升沿鎖存,下降沿數據輸出。

②片選信號(CSB),低電平開始通信周期并保持到通信周期結束,高電平時SDO和SDIO為高阻態。

③串行數據輸入/輸出口(SDIO),該引腳既可作為單向數據輸入口,也可作為雙向數據輸入輸出口,通過寄存器(0x00,bit7)控制,默認為單向數據輸入。

④串行數據輸出(SDO),作為數據輸出口,SDIO配置為雙向端口時,SDO為高阻態。

內部配置的任何改變會在最后一位寫入后立刻生效,因此,當有多個字節寫入到寄存器中時可以在一個通信周期中改變配置。同時,為了預防意外情況,改變寄存器配置時推薦使用單字節傳輸。

2.2 SPI接口操作

AD9779A的一個通信周期包括兩個階段。

第一階段是指令周期(向設備寫指令)與前8個SCLK的上升沿一致。指令字節規定串口控制器數據周期,也就是通信周期第二階段的數據傳輸是讀還是寫,數據傳輸的字節數和第一個寄存器的地址。每個通信周期的前8個SCLK上升沿用來向設備寫指令字節。

剩余的SCLK是通信周期的第二階段。第二階段是設備與MCU實際的數據傳輸階段。每次可以傳輸1~4個字節,傳輸的字節數由指令周期決定。寄存器在每個字節的最后一位寫入后立刻改變。

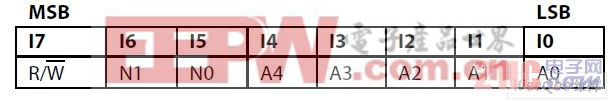

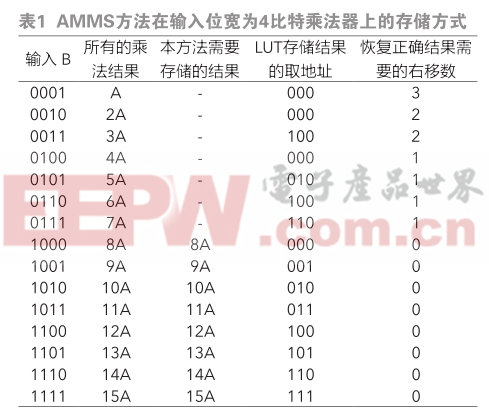

SPI指令如表1所列。

表1 SPI指令

,決定是讀操作還是寫操作。邏輯1讀操作。邏輯0寫操作。

N1和N0決定數據傳輸周期中傳輸的字節數。N1、N0表示的字節數如表2所列。

表2 N1、N0表示的字節數

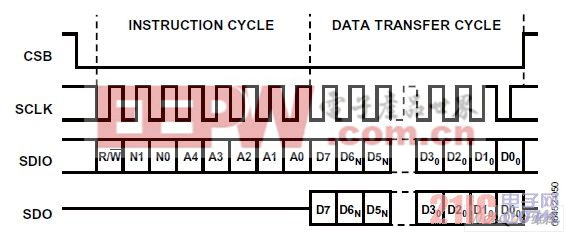

A4~A0確定在數據傳輸時哪個寄存器可以被訪問。在多字節傳輸時,這個地址是起始字節地址,其余寄存器地址由器件自動產生。最高位優先的寄存器配置時序如圖1所示。

圖1 最高位優先的寄存器配置時序如圖

評論