基于ISL5416的GPS/BD-2接收機DDC設計與實現

3 性能測試

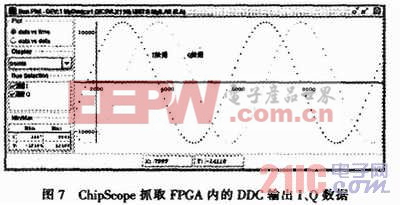

本系統采用AD6645高速ADC采集數據,并將數據輸入ISL5416。通過XILINX公司的XC5VLX110,百萬門級的FPGA接收DDC下變頻后數據。調試時,通過FPGA調試工具軟件ChipScope抓取FPGA內ADC數據及ISL5416輸出的I、Q兩路數據。FPGA內的DDC輸出I、Q數據如圖7所示。由圖可見,ISL5416正確地輸出了正交的I、Q兩路信號。

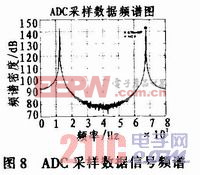

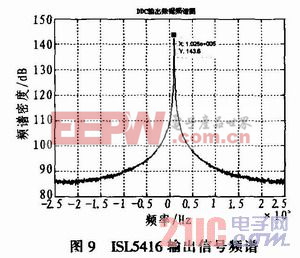

采用安捷倫信號發生器33250A產生67.52 MHz單頻正弦信號,在ADC采樣率為80 MHz時,采樣得到信號頻譜如圖8所示。信號經ISL5416下變頻之后得到I、Q兩路數據,I、Q兩路數據合成的復信號頻譜如圖9所示。

從以上兩圖可以看出,67.52 MHz單頻正弦經80 MHz采樣,ISL5416按上文所述的配置工作,頻譜搬移67.42 MHz,輸出正交的I、Q兩路信號,I、Q兩路信號的頻率為100 kHz,實現了頻譜的搬移,阻帶抑制符合要求,ISL5416正常工作,實現數字下變頻。

4 結 論

本文根據工程項目需求,結合4通道專用DDC芯片可靈活配置的特性,合理設計,將接收機中ADC采樣后的多載波中頻信號,通過DDC通道下變頻得到GPS和BD-2的I、Q數字基帶數據,以便后續的陣列信號處理及抗干擾算法研究。最終,使用8片DDC芯片ISL5416,實現了16陣元GP-S/BD-2接收機的DDC設計。由于此類接收機陣元數多,各通道結構一致,采用專用DDC芯片節約成本,也避免了采用FPGA設計DDC時的重復設計。為軟件無線電在16陣元GPS/BD-2接收機的實現提供了解決方案,并具有較強的商用價值。

評論