基于DDS的無線數據傳輸系統設計與實現

1.2 接收機電路

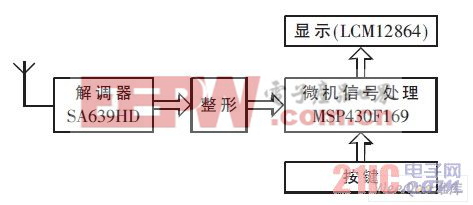

接收機硬件電路由解調電路、數據處理器、顯示電路及電源部分組成, 接收機框圖如圖2 所示。

圖2 接收機組成圖

解調器以飛利浦專用FSK 解調芯SA639DH 為核心部件。它具有靈敏度高、動態范圍大、傳輸速率快、穩定性好等特點。天線接收到的信號經輸入回路取出的2FSK信號與本振信號同時送入乘法器進行混頻, 再經一級帶通濾波器濾除高頻分量取其下變頻到中頻, 然后進行中頻放大后經二級帶通濾波送入限幅放大器進行限幅放大。限幅放大后的信號被分成兩路, 一路直接送入乘法器, 另一路經移相網絡移相90° 產生調相調頻波再送乘法器, 兩路信號進行相位比較, 乘法器輸出的信號經低通濾波器取出原調制信號, 然后再把該信號送入比較器進行整形后送信號處理器進行處理。

接收機數據處理器同樣采用MSP430F169 , 顯示器采用與發射機相同的LCM12864 。由于接收機部分與發射機相比功耗低, 故接收機電源部分采用兩節5 號干電池串聯供電。

2 系統軟件的實現

2.1 發射機的軟件設計

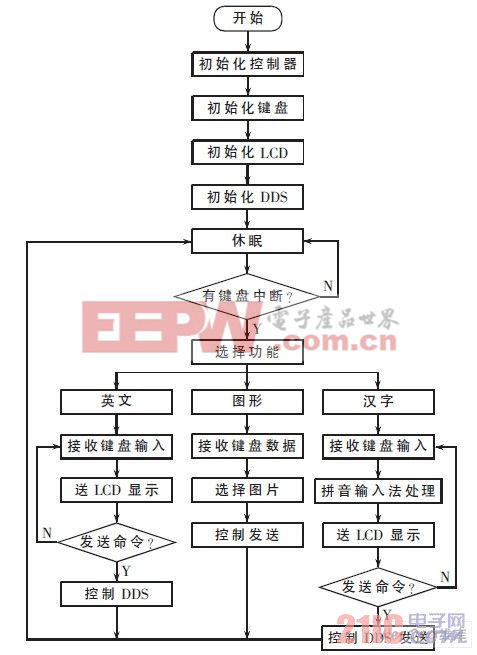

發射機上電后, 首先對系統進行初始化, 包括對控制器本身的端口配置、片內外設的配置, 以及外部的AD9854[ 6]、PS2 鍵盤和顯示器等部件的初始化。初始化結束后系統進入休眠模式, 直到被外部鍵盤產生的中斷喚醒。然后根據得到的按鍵鍵碼進行相應處理。為了讓AD9854 產生2FSK 信號, 需進行如下的初始化過程:S/PSELECT 置1 或置0 以決定輸入數據是并行還是串行。1為并行,0 為串行; 本系統采用串行接口, 在SCLK 信號控制下從并行輸入口D0~D1 寫入48 bit 并行寄存器, 或在SCLK 控制下從串行輸入口SDATA 寫入48 bit 串行寄存器。發射機的軟件流程圖如圖3 所示( 注: 在發射機內部存儲有3 幅圖片) 。

圖3 發射機流程圖

評論