基于TSI578的串行RapidIO交換模塊設計

1.3 時鐘設計

TSI578芯片需要3個時鐘源,其中一路156.25MHz差分對時鐘輸入(S_CLK_p/n)用來控制信號的傳輸速率,另一路100 MHz共模時鐘信號(P_CLK)用以控制TSI578內部寄存器的訪問。另外,由100 MHz的高穩晶振產生的時鐘信號經過驅動芯片后,其中一路可提供P_CLK時鐘,另外一路經過AD9516芯片產生所需的差分時鐘信號S_CLK_p/n。RapidIO數據的傳輸波特率可通過管腳,分別設置為1.25G、2.5G和3.125G。

1.4 復位設計

外部復位信號在輸入后,可與手動復位信號一起作為邏輯門的輸入,邏輯門的輸出連接至FPGA的復位控制管腳,從FPGA產生的復位信號可直接提供給TSI578以及其它芯片作為復位輸入。

2 基于信號完整性的高速電路板設計

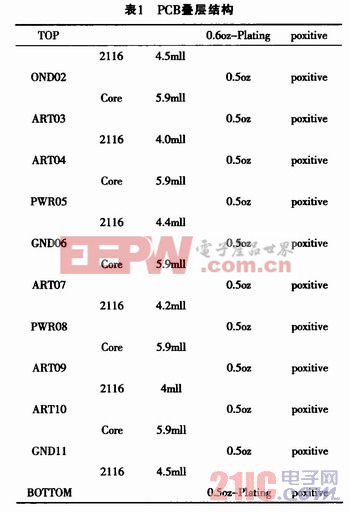

對于高速電路板來說,信號完整性問題是非常關鍵的一個問題。信號完整性設計包括兩個方面,一個是原理圖中的信號完整性設計,另一個是PCB中的信號完整性設計。在原理圖設計中,主要考慮反射和地彈效應。對于以上兩個效應的處理,可分別采用阻抗匹配和去耦電容兩種方法進行處理。為了更好的解決信號完整性問題,通常只局限于原理圖設計是遠遠不夠的,更多的工作還在PCB的設計中。PCB中的信號完整性分析包括布線前仿真和布線后仿真,前仿真是指在PCB布局、布線之前,對原理圖中的高速信號進行仿真,以考察信號在虛擬的疊層結構與布線參數下的傳輸效果,幫助設計者優化出一套適合當前電路的PCB疊層結構、布線阻抗與高速設計規則(線寬、線長、間距等)。后仿真則提供批處理仿真功能,它對PCB進行整板或關鍵網絡進行交互式仿真分析,輸出精確的信號波形、電磁輻射頻譜或眼圖,設計者可以修改布線參數后再仿真,從而發現并改善不合理的布線。本設計中的SRIO信號是關鍵的高速信號,根據PCB仿真結果設計出的PCB疊層結構和設計規則如表1和表2所列。本文引用地址:http://www.104case.com/article/156523.htm

評論