基于千兆以太網的高速數據傳輸系統設計

TCP/IP協議是一個協議族,集成有數據傳輸、流量控制、校驗、糾錯以及管理等多種功能。要通過網絡接口實現數據傳輸,沒有必要實現完整的TCP/IP協議,而且在有限的硬件資源上實現整個協議族也是不切實際的。圖1為TCP/IP協議族的分層結構,實現數據傳輸需要在每一層實現一種協議。應用層主要實現用戶控制,接收數據以及為發送數據做相應準備等。在運輸層,選擇UDP協議。UDP協議是面向無連接的,它提供不可靠的傳輸服務,不保證一定能將數據傳輸到目的地。而TCP協議是面向連接的,它提供可靠的傳輸服務,能保證正確的數據傳輸,協議中包括重傳機制、分片機制以及流量控制機制等。但UDP比TCP簡單的多,易于實現,占用資源也比較少。在網絡層,選擇IP協議和部分ICMP協議。IP協議用于數據傳輸,而ICMP協議用于測試,如ping命令就屬于ICMP協議。在鏈路層,需要有MAC控制器實現以太網數據幀的打包解包、校驗和計算等。另外,還需要實現ARP協議。ARP協議用于通知通信雙方各自的硬件地址信息。

2 方案選擇及實現

2.1 千兆以太網的設計方案研究

千兆以太網的關鍵技術在于千兆以太網的MAC控制器和以太網接口的實現。目前市場上物理層芯片和MAC芯片都比較多,但大多數MAC芯片是PCI或PCIe接口,這種芯片主要用于計算機主板,而GMII接口的MAC芯片接口簡單,便于用戶使用。對于不同的系統,設計千兆以太網的方法應根據系統的處理器類型而定,目前主流的處理器有FPGA、DSP、SOC、PowerPC等,根據處理器類型,大致可分為以下3種:

(1)使用FPGA作為主控制器,可以使用一片物理層協議芯片實現物理層,一片MAC芯片實現MAC層,而上層協議在FPGA內部使用硬件描述語言實現。也可以在FPGA內部使用MAC核代替MAC芯片,從而簡化系統設計。如Xilinx Virtex-5系列FPGA中就集成有10/100/11 000 Mb·s-1以太網MAC控制器硬核,而Altera提供Triple Speed EthemetMegaCore軟核控制器。

(2)使用集成有MAC控制器的DSP芯片,外部使用物理層芯片來實現物理層。如TI公司的TMS320C647x系列DSP,它采用哈佛總線結構,集成

度較高,運算速度快。可以完全使用C語言編程,操作方便。

(3)使用基于嵌入式操作系統的TCP/IP協議棧,如PowerPC芯片,它可以嵌入某些操作系統,如Linux系統,能夠方便的實現TCP/IP控制,外部使用一片物理層芯片即可。由于有TCP/IP協議棧的支持,省去了編寫協議的工作。

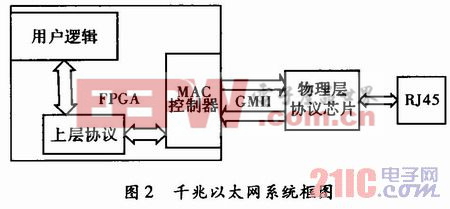

在系統中,主控制芯片選擇Altera公司的StratixlI系列FPGA,StratixII系列FPGA片資源豐富,支持多種電平標準,并集成有M4K,M512等多種形式的存儲器資源,可以實現數據的緩沖及存儲。MAC控制器使用該公司提供的MAC軟核來實現,該軟核支持多款物理層芯片,選擇NI公司的DP83865芯片,系統如圖2所示。本文引用地址:http://www.104case.com/article/156459.htm

此方案較其他方案有明顯的優勢。(1)DP83865采用GMII接口,簡單易用,而且性價比很高,與Altera公司的MAC軟核一起使用上簡化了設計者的工作,能有效縮短產品開發周期。(2)MAC軟核在FPGA內部占用的邏輯資源較少,所以并不會增加系統的額外開銷。

2.2 物理層芯片介紹

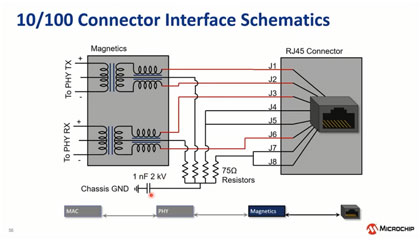

DP83865支持10Base-T/100Base-Tx/1000Base-T以太網協議,它使用0.18 μm、1.8 V CMOS工藝,使用MII、GMII或RGMII的媒體獨立接口,簡化了與MAC控制器的連接,具有超低功耗、完全自適應等特點,便于用戶實現10/100/1 000 Mb·s-1以太網。芯片內部設有32個寄存器,可以通過MDIO接口訪問其內部寄存器。Altera公司的MAC軟核內部映射有兩個物理層芯片的寄存器組空間,其地址空間與DP83865內部寄存器一一對應,用戶可以通過訪問MAC軟核內部寄存器以達到訪問DP83865的寄存器目的,MAC軟核將自動通過MDIO接口訪問DP83865的寄存器。這樣,如果要重新設定DP83865內部寄存器值,或者在調試過程中要通過讀取寄存器來判斷芯片的工作狀態,可以直接訪問其在MAC軟核內部映射的寄存器空間,從而簡化設計。

tcp/ip相關文章:tcp/ip是什么

評論