一種ZigBee電力無線抄表數據收發終端設計

3 收發終端硬件設計

該終端系統主要包括:電表數據收集電路、無線發送電路和電源電路3部分。

(1)電表數據收集電路主要是MCU控制電路,處理RS 485發送過來的數據。主要有MCU芯片,RS 485控制芯片、光耦隔離器、時鐘電路、穩壓電路等構成。

(2)無線發送電路主要是通過SPI接口接收MCU的處理數據,通過RF射頻天線發送。

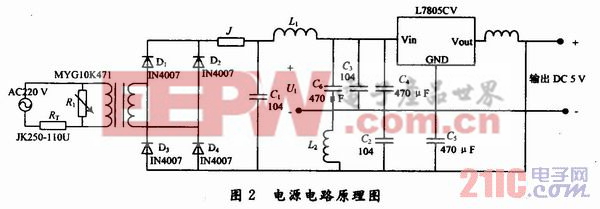

(3)電源電路主要是完成將交流220 V電壓轉化成直流電壓,再通過穩壓等完成對系統的供電。主要由小型變壓器、熱敏電阻、壓敏電阻器、穩壓芯片等構成。

系統主要器件選型:

MCU:選用Ateml公司的ATmega 64L芯片,是一款基于支持實時仿真的高性能、低功耗的8位RISC結構的AVR微控制器。帶有64 KB系統內可編程FLASH,4 KB的片內SRAM,64 KB可選外部存儲空間,32個通用寄存器,實時計數器(RTC),4個具有比較模式與PWM的靈活定時器/計數器(T/C),2個USART,面向字節的兩線串行接口,8路10位具有可選查分輸入級可編程增益的ADC,看門狗定時器,一個SPI接口,JTAG接口,以及6個可以通過軟件進行選擇的省電模式,滿足無線抄表系統中對可靠性和功耗的要求。

ZigBee芯片:選用TI公司的CC2430 RF,其是一顆真正的系統芯片,提倡CMOS解決方案,這種解決方案能夠提高性能并能滿足以ZigBee為基礎的2.4GHz ISM免費波段的應用,同時滿足低成本,低功耗的要求。它結合一個高性能2.4 GHz DSSS(直接序列擴頻)射頻收發器核心和一顆工業級小巧高效的8051控制器,收發波特率250 Kb/s。CC2430在接收和發射模式下,電流損耗分別為27 mA或25 mA。CC2430的休眠模式和轉換到主動模式的超短時間的特性,特別適合無線抄表這種要求電池壽命比較長的應用。接收數據時,當CC2430全部收到幀開始定界符SFD后,IRQ_SFD(中斷標志位寄存器)置1;當RXFIFO中有數據時,RFSTATUS.FIFO置1,數據為空時,置0;當RXFIFO中未讀過的字節超過編程設置在IOCFG0.FIFOP_THRRF_P的閾值時,RFSTATUS.FIFOP置1,反之,置0。RF_N兩個引腳顯示接收和發送數據狀態,RF_P引腳:接收時,正RF(射頻)輸入信號到LNA(低噪聲放大器);發送時,接收來自PA(功率放大器)的正RF(射頻)信號。RF_N引腳:接收時,負RF(射頻)輸入信號到LNA(低噪聲放大器);發送時,接收來自PA(功率放大器)的負RF(射頻)信號。CC2430通過SPI接口接收ATmega64L的時鐘信號和片選信號,

由內部集成的8051核完成數據信號的處理和輸入/輸出操作,從而完成電表數據的傳輸。

片外FLASH:用來存儲電表數據,選用金士頓1 GB SD卡,由于電源電路的輸出電壓為5 V,而SD卡需3.3 V供電,所以要將電壓轉換,用SE8117T33輸出3.3 V電壓,接到SD卡VDD引腳上。

時鐘芯片:選用Philips公司的實時時鐘芯片PCF8563T,是一種低功耗CMOS時鐘芯片,提供一個可編程輸出、終端輸出和掉電檢測器,所有地址和數據都通過I2C總線接口串行傳輸,得到最大的總線傳輸速度。

光電耦合器:選用本系統選用3個PC817光電耦合器,用來隔離上下級電路,減小電路干擾,簡化電路設計。PC817是一種單通道線性光耦,能夠傳輸連續變化的模擬電壓和電流信號。

穩壓芯片:選用L7805CV,是電源電路設計中常用的性能很好的穩壓芯片。該設計中MCU控制電路和電源電路都用到穩壓芯片,是電路能得到穩定的5 V電壓。電源電路原理圖如圖2所示。本文引用地址:http://www.104case.com/article/156340.htm

圖2中R1電阻選用MYG 10K471壓敏電阻器,主要做保護電路器件。

4 軟件設計流程

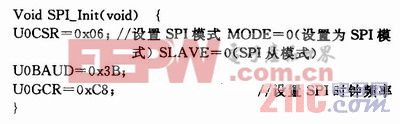

該系統軟件主要是MCU控制電路的初始化程序設計,ZigBee無線模塊的初始化、接收和發送程序設計,初始化程序主要是對單片機、RF芯片、SPI等進行初始化;SPI初始化程序如下:

評論