CPCI數(shù)據(jù)總線接口的設(shè)計與實(shí)現(xiàn)

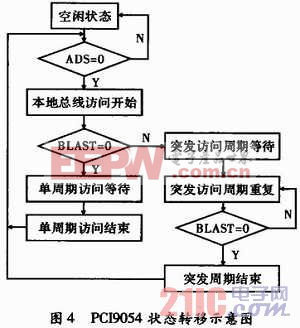

FPGA內(nèi)部邏輯要設(shè)計本地端總線控制模塊,實(shí)現(xiàn)局部總線的狀態(tài)控制,同時產(chǎn)生片內(nèi)的讀寫時序及地址信號以支持突發(fā)傳輸和單周期傳輸,因此使用Verilog HDL語言中的狀態(tài)機(jī)來完成上述功能。其狀態(tài)轉(zhuǎn)換,如圖4所示。本文引用地址:http://www.104case.com/article/156072.htm

5 測試結(jié)果

利用SingnalTap采集到的單周期時序傳輸圖,如圖5所示。

6 結(jié)束語

以PCI9054為核心介紹了CPCI板卡與嵌入式CPU板卡之間高速數(shù)據(jù)通信系統(tǒng)接口的軟硬件設(shè)計。PCI9054因其靈活和方便的接口功能,使操作者只需關(guān)心LOCAL BUS接口電路的時序設(shè)計,并且利用其傳輸速率高的特性,可以幫助一些對實(shí)時性要求較高的系統(tǒng)解決其傳輸數(shù)據(jù)的問題。

評論