基于DSP的16通道聲發射同步數據采集電路設計

2.2 VC5509A與ADS1278數據接口電路設計

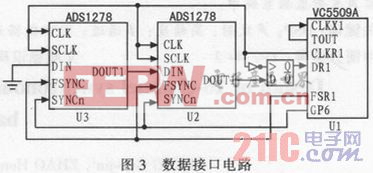

ADS1278轉換后的數據以串行方式通過引腳輸出,可以通過FORMAT[2:0]來選擇傳輸協議和數據格式。本文通過VC5509A的McBSP外設接口來接收ADS1278轉換后的數據,該接口同時支持SPI和幀同步協議,能夠方便的實現ADS1278的無縫連接。相比較而言,幀同步模式擁有更快的傳輸速度,所以本文選擇了幀同步協議。

VC5509A與ADS1278采用幀同步協議的數據接口電路如圖3所示,兩片ADS1278以菊花鏈的方式級聯。其中,U3的輸入DIN接地,DOUT1連到U2的DIN輸入;U2的輸出DOUT1經D觸發器后連到VC5509A的DR1引腳;U2和U3擁有相同的CLK、SCLK、SYNCn和FSYNC控制信號。

2.3 電源和基準電路設計

穩定、低噪聲的電源是實現高精度數據采集的必要保證,該數據采集電路包含3種典型電源:ADS1278的1.8 V內核電源,3.3 V I/O口電源和5 V模擬電源。其中,5 V模擬電源通過具有較小紋波的LM7805線性穩壓得到:3.3 V和1.8 V數字電源通過具有高電源抑制比和低噪聲性能的電源芯片TPS73033和TPS73018獲得。

基準電路在高精度數據采集電路的設計中起著至關重要的作用,它會直接影響到數據采集電路的精度和穩定性。本文采用了TI公司的一款低噪聲、低溫漂、精度極高的電壓基準芯片REF5025為ADS1278提供參考電壓。為使REF5025的輸出性能達到最佳,在將基準信號送入ADS12 78之前添加了一級調理電路,用于進行阻抗匹配和濾波。

3 數據采集電路的底層軟件實現

數據采集電路的底層軟件實現包括配置和數據采集兩部分。其中,配置又可分為兩部分:一是對VC5509A本身的初始化,包括:CSL庫、PLL、GPIO、I2C、定時器、McBSP、DMA和中斷等:二是對ADS1278參數的設置,包括通道開啟情況、工作模式和采樣率等。數據采集工作主要是由DMA來完成的,CPU只負責切換緩沖區和處理數據等操作。

數據采集電路的底層軟件工作流程如圖4所示。系統上電后,首先完成初始化和ADS1278的配置工作;然后,CPU發出同步轉換脈沖,啟動數據轉換,進入中斷等待狀態;與此同時由DMA來進行數據采集,當DMA存滿緩沖區后觸發中斷;CPU進行切換緩沖區和數據處理等操作,然后返回等待下一次中斷。

在上述過程中,DMA和CPU是并行工作的:即DMA專門負責存儲數據,將數據搬移到緩沖區:而CPU則負責切換緩沖區并處理緩沖區內的數據。但同一時刻,CPU和DMA操作的是不同的緩沖區:當DMA向緩沖區0存儲數據時,CPU處理緩沖區1的數據:而DMA向緩沖區1存儲數據時,CPU

處理緩沖區0的數據。這樣DMA和CPU實現了一種“乒乓”切換操作,使得DSP能夠更加專注于數據處理,從而能夠發揮最佳性能。

評論