基于以太網硬件協仿真接口實現便捷和高帶寬的仿真

通常情況下,在設計基于FPGA的大型信號處理系統的時候,設計人員往往需要進行費時費力的仿真。以Xilinx System Generator for DSP為代表的FPGA設計工具,通過提供可靠的硬件在環接口(該接口可以直接將FPGA硬件置入設計仿真),來解決這種問題。

通過在硬件上模擬部分設計,這些接口可以大大提高仿真的速度——通常可以提高一個甚至多個數量級。使用硬件在環還可以讓設計人員實時進行FPGA硬件調試和驗證。

System Generator for DSP 可以為多類FPGA開發平臺提供硬件在環接口。這些平臺通常通過不同的物理接口和PC建立通信。舉例來說,一個JTAG協仿真接口可以允許任何一個具備JTAG頭和Xilinx FPGA的FPGA板在System Generator for DSP內部進行協仿真。其它類型的板卡,比如XtremeDSPTM開發工具套件,是通過PCI總線進行通信的。直到最近以來,具有高存儲帶寬和吞吐率要求的系統協仿真(例如視頻和圖像處理),還只能在那些通過PCI或者是PCMCIA接口直接與PC建立通信的開發板上進行。

基于以太網的協仿真

System Generator for DSP 8.1內含一個全新的以太網協仿真接口,該接口首次讓Xilinx ML402 評估平臺具備了高帶寬協仿真的能力。ML402開發板將直接通過標準以太網電纜或者通過網絡遠程連接到計算機上。

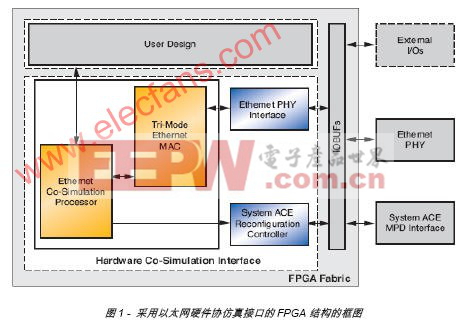

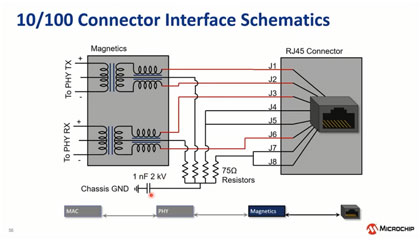

接口的核心是Xilinx三態以太網MAC核,它可以支持10/100/1000 Mbps半雙工和全雙工操作模式。當設計人員通過使用以太網硬件協仿真接口生成一個設計的時候,System Generator for DSP將自動在設計周圍建立必要的邏輯,從而在仿真的過程中,通過以太網連接與FPGA進行通信(圖1)。 你還可以雙擊任意一個設計的System Generator模塊打開它的參數配置對話框,從而生成一個用于以太網硬件協仿真的設計。在編譯菜單下,從硬件協仿真菜單中選擇ML402/Ethernet編譯(參見圖2)。你可以在兩種不同的以太網協仿真模式中進行選擇。

基于網絡的協仿真

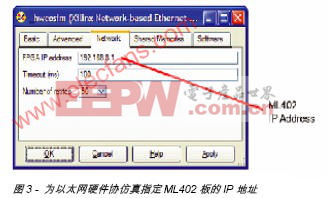

基于網絡的接口可以讓開發人員對那些連至標準IPv4網絡的FPGA硬件進行協仿真。由于IPv4這種網絡幾乎無處不在,基于網絡的接口,為與連接至有線或者無線網絡的遠程FPGA開發板建立通信提供了一條便捷的途徑。該接口在后臺管理著通信細節和錯誤處理過程(在丟包后重新進行傳送)。System Generator for DSP通過分析ML402板的IP地址來決定在協仿真過程中與哪個平臺進行通信(圖3)。

評論