一種基于AD9854的BPSK信號(hào)產(chǎn)生設(shè)計(jì)

相位寄存器配置值的計(jì)算公式為(φ/2π)×214,其中φ為需要配置的相位值,對(duì)于BPSK信號(hào),一般1號(hào)相位寄存器表示的相位值與2號(hào)相位寄存器表示的相位值相差π。頻率寄存器配置值的計(jì)算公式為(f/fs)×248,其中f是需要輸出的BPSK載頻,即中頻頻率;fs為系統(tǒng)時(shí)鐘頻率,它由從REFCLK得到的外部參考時(shí)鐘頻率經(jīng)可編程參考時(shí)鐘倍頻器倍頻后得到。需要考慮的控制寄存器各比特定義和配置值如表2所示。本文引用地址:http://www.104case.com/article/153520.htm

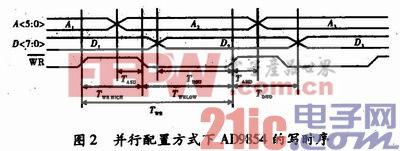

AD9854工作于并行配置方式下的寫(xiě)時(shí)序,如圖2所示,圖中最大時(shí)延TWRHGH為7ns,在編寫(xiě)程序時(shí)需要注意時(shí)延量。

最后的控制步驟就是編寫(xiě)軟件,用FPGA對(duì)AD9854進(jìn)行控制可以通過(guò)狀態(tài)機(jī)的方式實(shí)現(xiàn)。

(1)采用Verilog HDL語(yǔ)言定義FPGA的管腳如下

modulate AD9854_Control(

input clk10MHz,

output reg[5:0]a=6'h00,

output reg[7:0]d=8'h00,

output regwrb=1’b1,

output regud=1'b0,

output regbpsk=1'b0,

output wirerefclk);

(2)給出refclk的頻率為10MHz

assign refclk=clk10MHz;

評(píng)論