基于SOPC的數據發生系統設計

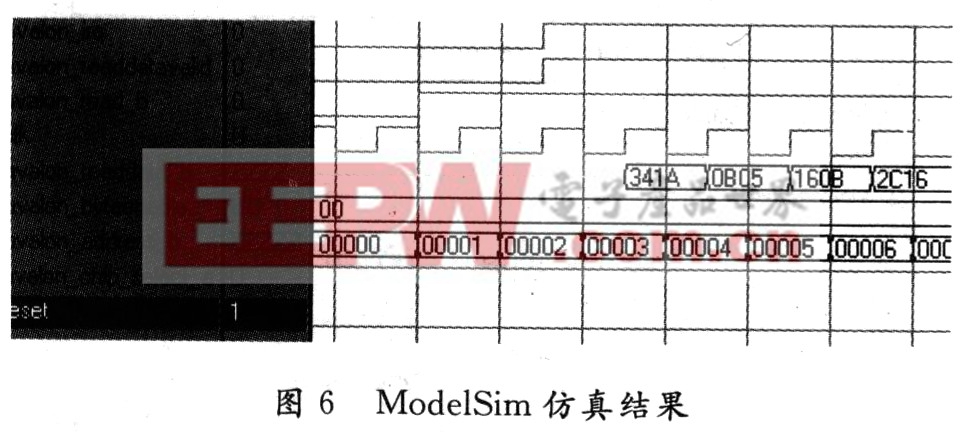

數據產生,乒乓結構和兩片SRAM三部分的組合在ModelSim中的仿真結果如圖6所示。avalon_ad-dress_b不變時是在執行第一次寫操作,此時沒有數據讀出,所以avalon_readdata_b值為高阻;avalon_ad-dress_b開始變化時,表示一片SRAM已經寫滿,正在執行該片的讀操作,而另一片在執行寫操作,avalon_readdata_b為系統生成的數據。

2.3 PCI9054接口邏輯模塊

PCI總線作為PC機與外部設備之間重要的連接總線,具有數據傳輸穩定靈活,傳輸速度快,即插即用和良好的擴展性等特點,被廣泛地用在各種與PC機互聯的設備中。該系統采用的PCI9054芯片口可以將復雜的PCI總線接口轉換為相對簡單的用戶接口,大大縮短了設計周期。

2.3.1 本地總線狀態機設計

由于PCI9054的DMA傳輸方式只適宜于做單次傳輸,故該系統采用了DMA結合中斷的方式傳輸數據。由于數據的存儲采用了乒乓結構,可以在一片SRAM執行DMA傳輸的同時執行另一片寫操作,這樣不會造成數據丟失,狀態也比較容易控制。

系統復位后,數據產生模塊開始產生偽隨機序列,產生的數據直接存入SRAM中。此時,計數器同步計數,當計數值每一次達到262 144時,也就是一片SRAM已經存滿時,SOPC系統就會觸發PCI9054中斷請求信號LINT#,CPU響應中斷,發出讀命令、要讀取的字節數、地址信號等。PCI9054:先通過LHOLD申請本地總線的控制權,SOPC系統通過LHOLDA響應,使PCI9054.獲得本地總線的控制權。PCI9054將PCI地址空間映射到本地地址空間,接著啟動本地總線的DMA傳輸。

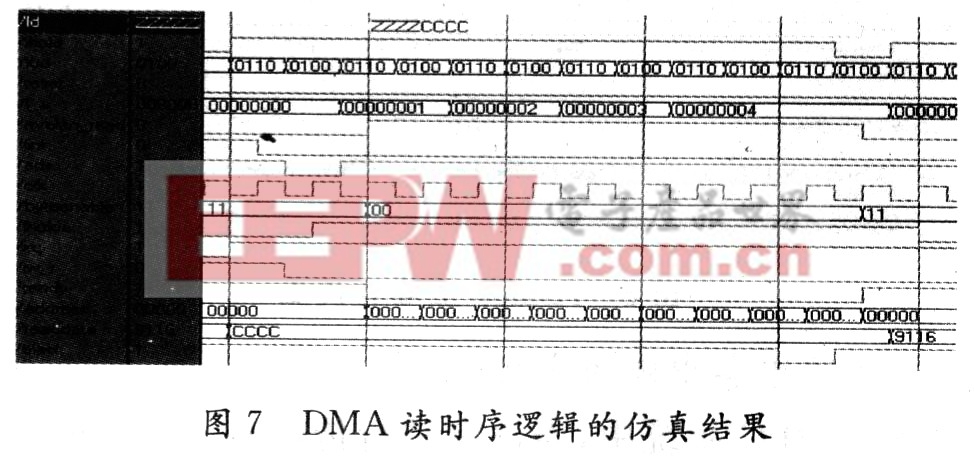

該系統采用VHDL語言,實現了DMA讀傳輸本地端的時序控制狀態機設計。狀態0為空閑狀態(i-dle),若LHOLD信號被置1,則轉到狀態1,否則留在狀態0。狀態1為總線保持狀態(hold),在此狀態下應將LHOLDA信號置l。如果信號ADs為O且LW_R為0,則轉到狀態2。狀態2為DMA讀狀態(DMA_read),在此狀態下應將READY信號和模塊內部信號avaIon_read置l,從而使AvaIon主端口的master_read置1,表示Avalon主外設發起讀傳輸。如果BLAST為1,則表明此次DMA讀取還沒有完成,繼續留在狀態2;如果BLAsT為0,則表明此次DMA讀取完成,轉到狀態3。狀態3為DMA讀操作完成狀態(end cycle),當LHOLD被置0時,表示PCI9054不再請求本地總線,則轉到狀態0;當BLAST為0且LHOLD為1時,則表明PCI9054還要進行DMA讀操作,則轉到狀態1繼續。其中的DMA讀操作的時序邏輯的ModelSim仿真結果如圖7所示。

2.3.2 Avalon主外設的端口信號設計

該系統中,PCI9054控制數據從本地總線上讀出,先到PCI9054的FIFO中,再將FIFO中的數據傳輸到PCI總線上。因此SOPC系統中的PCI9054接口邏輯模塊為Avalon主外設,主端口通過address,read,wait-request等信號發起Avalon總線上的讀操作,從而控制Avalon從外設即乒乓結構模塊的讀操作。

由于本系統定制的從外設采用了流水線讀的傳輸模式,為了使端口傳輸模式匹配,主外設也采用流水線讀的傳輸模式。流水線主端口一個必須的信號為readdatavalid,Avalon交換結構向主端口發出readdat-avalid,以表示readdata信號正在提供有效的數據。

本系統定制的Avalon主外設構成模塊主要由5部分構成,其中Read Master Logic提供了符合Aval-on接口規范的主端口信號;Control Logic是ReadMaster Logic與PCI9054 Local Bus Logic控制信號和狀態信號轉換的橋梁;FIFO是數據由Read MasterLogic向PCI9054傳輸的緩沖區。這三部分通過主端口流水線讀傳輸時序邏輯聯系在一起,提供了Avalon主外設的主端口接口界面。PCI9054 Local Bus Logic即VHDL語言設計的本地總線狀態機,它將PCI9054本地端的信號通過狀態機邏輯轉換為與Control Logic和FIFO相對應的信號;Clock/Reset提供了主外設的clk和reset信號。

光耦相關文章:光耦原理

萬用表相關文章:萬用表怎么用

斷路器相關文章:斷路器原理

負離子發生器相關文章:負離子發生器原理 高壓真空斷路器相關文章:高壓真空斷路器原理 塵埃粒子計數器相關文章:塵埃粒子計數器原理 漏電斷路器相關文章:漏電斷路器原理

評論