基于Nios II的AT24C02接口電路設計

2.2 AT24C02A器件讀寫時序

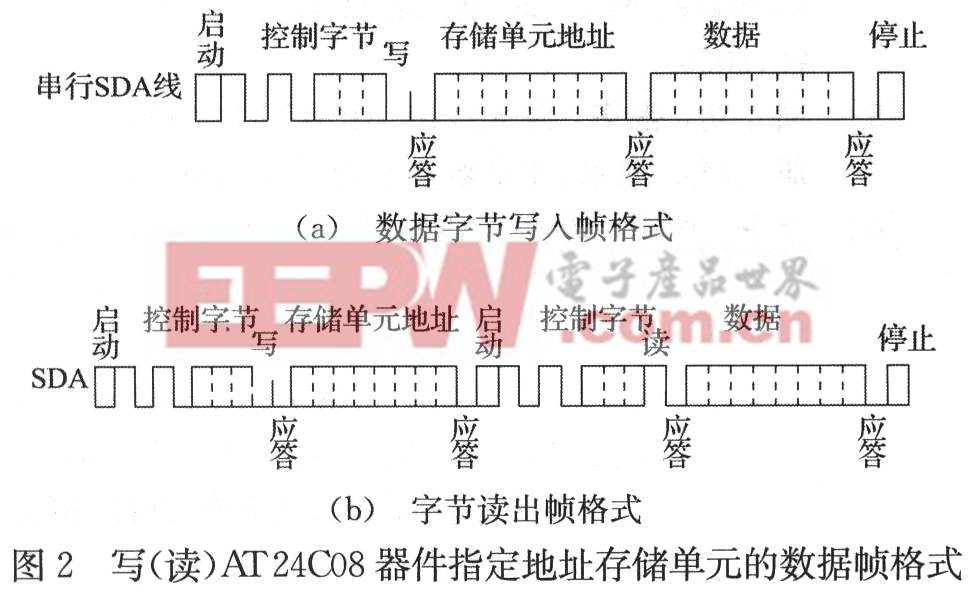

圖2為寫(讀)AT24C02A器件中指定地址存儲單元的數據幀格式,圖2(a)為寫操作的幀格式,(b)為讀操作幀格式。要想把一個字節數據發送到器件中(或從器件中讀取一個字節數據)除了給出具體的地址信息之外,還要給出該器件的控制信息:首先由控制器發出“啟動”信號,啟動I2C總線的通信,然后發送一個控制字節,前7位為器件的片選地址,最后1位為讀寫控制位,“0”表示寫,“1”表示讀。當傳完控制字節之后,掛在I2C總線的所有的器件比較控制字節片選地址(前7位)是否與自已的物理地址一致,如一致,則發一個應答信號。控制器接收到應答信號之后,再發器件內部存儲單元地址和其他的信息。

3 AT24C02A讀寫控制接口設計

3.1 寄存器組定義

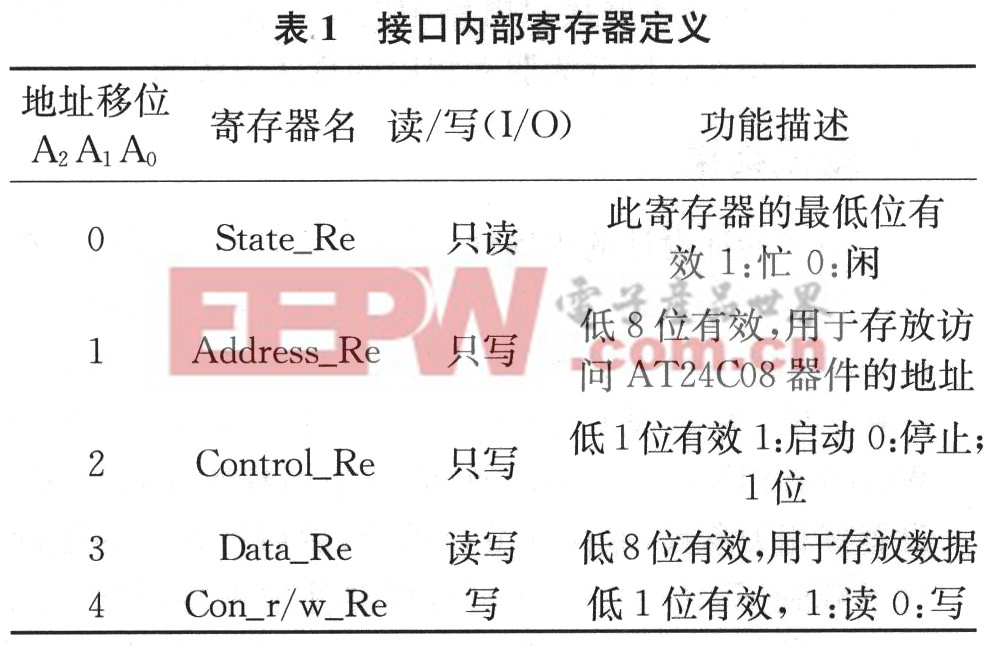

為了實現NiosⅡI能與外部設備進行交換數據,首先要在AT24C08讀寫控制接口中定義寄存器,包括數據寄存器、狀態寄存器和控制寄存器。表4-1AT24C02A讀寫控制器內部寄存器定義的情況:State_Re為此接口電路的狀態寄存器,最低位有效,用來表示接口電路的狀態,“1”表示接口處于“忙”狀態中,此時表示接口正處于讀寫外部設備(AT24C02A)中,不能對此控制接口進行操作,只到接口處于“0”狀態時為止;Address_Re為數據寄存器,用于存放NiosⅡ要訪問AT24C02A器件內部單元的地址數據;Control_Re為控制寄存器,控制著接口電路啟動或停止,“1”為啟動,“0”停止;Data_Re為數據寄存器,用于存放傳輸的數據;Con_r/w_Re為控制寄存器,控制數據的傳輸方向,高電平為讀(輸入),低電平為寫(輸出)。

3.2 邏輯功能模塊設計

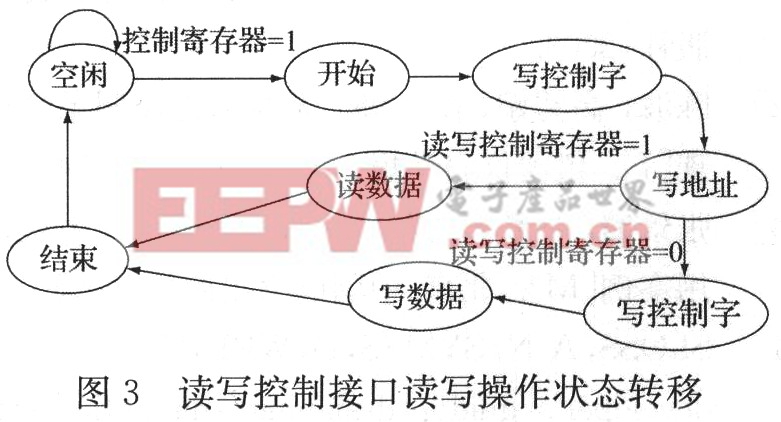

在接口電路中,除了定義接口電路的寄存器組之外,還要利用硬件描述語言來描述接口電路要實現的功能,即邏輯功能模塊的設計。接口電路要完成的主要功能是,用接口電路產生如圖3所示的時序,成功讀寫外部存儲器件。在本設計中,采用了有限狀態機來實現這一功能,圖4為本設計的各個狀態之間轉換狀態圖:當NiosⅡ要交換數據時,首先要讀State_Re的值,并判定電路是否為“空閑”狀態,只有狀態機處在空閑狀態,才允許進行一次讀寫操作,并修改狀態寄存器的值為“忙”狀態;當完成一次讀寫操作時,修改狀態寄存器的值為“閑”狀態。

評論