嵌入式系統低功耗設計研究

2.8 降低處理器的時鐘頻率

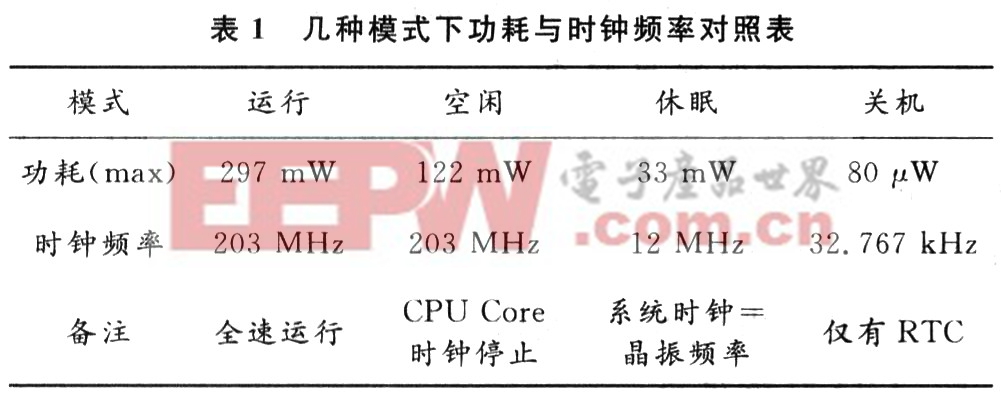

處理器的功耗與時鐘頻率密切相關。以SAM-SUNG S3C2410x(32 b ARM 920T內核)為例,它提供了四種工作模式:正常模式、空閑模式、休眠模式、關機模式.各種模式的功耗如表1所示。本文引用地址:http://www.104case.com/article/152201.htm

由表1可見,CPU在全速運行的時候比在空閑或者休眠的時候消耗的功率大得多。省電的原則就是讓正常運行模式遠比空閑、休眠模式少占用時間。在類似PDA的設備中,系統在全速運行的時候遠比空閑的時候少,所以可以通過設置,使CPU盡可能工作在空閑狀態,然后通過相應的中斷喚醒CPU,恢復到正常工作模式,處理響應的事件,然后再進入空閑模式。因此設計系統時,如果處理能力許可,可盡量降低處理器的時鐘頻率。

另外,可以動態改變處理器的時鐘,以降低系統的總功耗。CPU空閑時,降低時鐘頻率;處于工作狀態時,提高時鐘頻率以全速運行處理事務,實現這一技術的方法。通過將I/O引腳設定為輸出高電平,加入電阻R1,將增加時鐘頻率;將I/O引腳輸出低電平,去掉電阻R1,可降低時鐘頻率,以降低功耗。

2.9 降低持續工作電流

在一些系統中,盡量使系統在狀態轉換時消耗電流,在維持工作時期不消耗電流。例如。IC卡水表、煤氣表、靜態電能表等,在打開和關閉開關時給相應的機構上電,開關開和關狀態通過機械機構或磁場機制保持開關的狀態,而不通過電流保持,可以進一步降低電能的消耗。

3 軟件低功耗設計

3.1 編譯低功耗優化技術

編譯技術降低系統功耗是基于這樣的事實:對于實現同樣的功能,不同的軟件算法,消耗的時間不同,使用的指令不同,因而消耗的功率也不同。對于使用高級語言,由于是面向問題設計的,很難控制低功耗。但是,如果利用匯編語言開發系統(如對于小型的嵌入式系統開發),可以有意識地選擇消耗時間短的指令和設計消耗功率小的算法來降低系統的功耗。

3.2 硬件軟件化與軟件硬件化

通常的硬件電路一定消耗功率,基于此,可以減少系統的硬件電路,把數據處理功能用軟件實現,如許多儀表中用到的對數放大電路、抗干擾電路,測量系統中用軟件濾波代替硬件濾波器等。

需要考慮,軟件處理需要時間,處理器也需要消耗功率,特別是在處理大量數據的時候,需要高性能的處理器,這可能會消耗大量的功率。因此,系統中某一功能用軟件實現,還是用硬件實現,需要綜合計算后進行設計。

3.3 采用快速算法

數字信號處理中的運算,采用如FFT和快速卷積等,可以大量節省運算時間,從而減少功耗;在精度允許的情況下,使用簡單函數代替復雜函數作近似,也是減少功耗的一種方法。

3.4 軟件設計采用中斷驅動技術

整個系統軟件設計成處理多個事件,在系統上電初始化時,主程序只進行系統的初始化,包括寄存器、外部設備等,初始化完成后,進入低功耗狀態,然后CPU控制的設備都接到中斷輸入端上。當外設發生了一個事件,產生中斷信號,使CPU退出節電狀態,進入事件處理,事件處理完成后,繼續進入節電狀態。

3.5 延時程序設計

延時程序的設計有兩種方法:軟件延時和硬件定時器延時。為了降低功耗,盡量使用硬件定時器延時,一方面提高程序的效率,另一方面降低功耗。原因為:大多數嵌入式處理器在進入待機模式時,CPU停止工作,定時器可正常工作,定時器的功耗可以很低,所以處理器調用延時程序時,進入待機方式,定時器開始計時,時間一到,則喚醒CPU。這樣一方面CPU停止工作,降低了功耗,另一方面提高了CPU的運行效率。

4 結 語

嵌入式系統的設計涉及到軟件設計和硬件設計兩個方面,在實際系統應用時,低功耗的設計并非是一蹴而就的事情,需要綜合考慮各種可能的因素、條件和狀態,需要對各種細節進行認真的斟酌和分析,需要對各種可能的方案和方法進行計算和分析,這樣才可能取得較為滿意的效果,達到降低系統功耗的目的。

評論