AD9833型高精度可編程波形發(fā)生器設計方案

AD9833是可編程波形發(fā)生器,能夠產生正弦波、三角波、方波輸出。波形發(fā)生器廣泛應用于各種測量、激勵和時域響應領域,AD9833無需外接元件,輸出頻率和相位都可通過軟件編程,易于調節(jié),頻率寄存器是28位的,主頻時鐘為25MHz時,精度為0.1Hz,主頻時鐘為1MHz時,精度可以達到0.004Hz。

可以通過3個串行接口將數據寫入AD9833,這3個串口的最高工作頻率可以達到40MHz,易于與DSP和各種主流微控制器兼容。AD9833的工作電壓范圍為2.3V-5.5V。

AD9833還具有休眠功能,可使沒被使用的部分休眠,減少該部分的電流損耗,例如,若利用AD9833輸出作為時鐘源,就可以讓DAC休眠,以減小功耗,該電路采用10引腳MSOP型表面貼片封裝,體積很小。

AD9833的主要特點如下:

頻率和相位可數字編程;

工作電壓為3V時,功耗僅為20mW;

輸出頻率范圍為0MHz-12.5MHz;

頻率寄存器為28位(在25MHz的參考時鐘下,精度為0.1Hz);

可選擇正弦波、三角波、方波輸出;

無需外界元件;

3線SPI接口;

溫度范圍為-40℃-+105℃。

2 AD9833的結構及功能

2.1 電路結構

AD9833是一塊完全集成的DDS(Direct Digital Frequency Synthesis)電路,僅需要1個外部參考時鐘、1個低精度電阻器和一個解耦電容器就能產生高達12.5MHz的正弦波。除了產生射頻信號外,該電路還廣泛應外于各種調制解調方案。這些方案全都用在數字領域,采用DSP技術能夠把復雜的調制解調算法簡化,而且很精確。

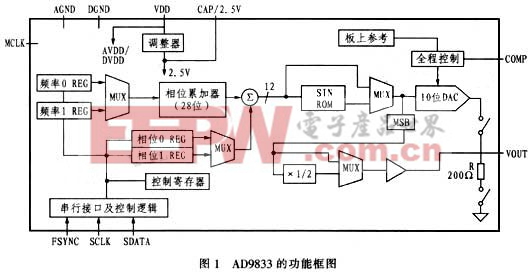

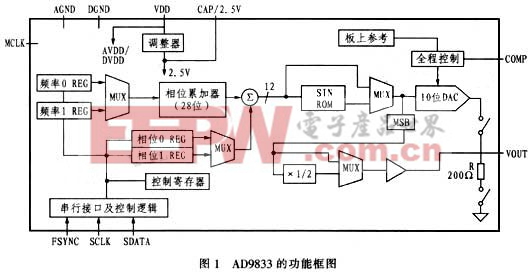

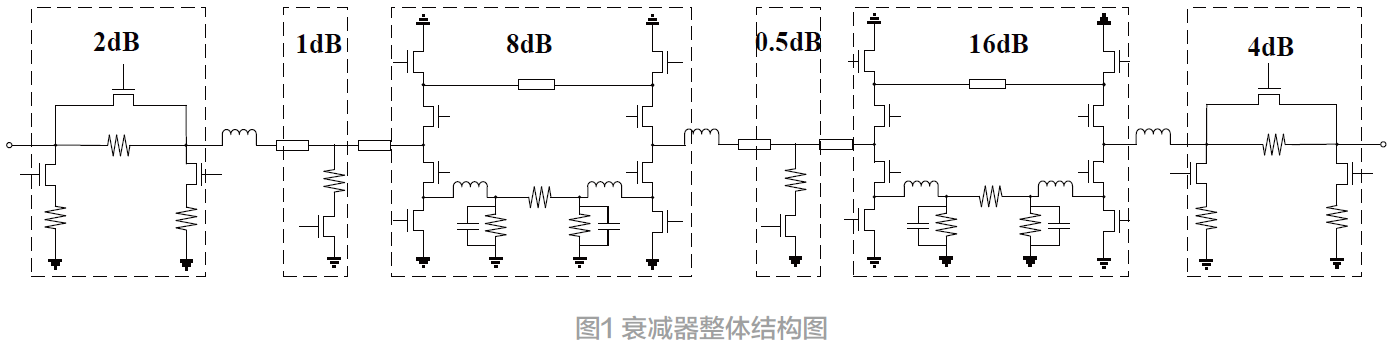

AD9833的內部電路主要有數控振蕩器(NCO)、頻率和相位調節(jié)器、Sine ROM、數模轉換器(DAC)、電壓調整器,其功能框圖如圖1所示。

AD933的核心是28位的相位累加器,它由加法器和相位寄存器組成,每來1個時鐘,相位寄存器以步長增加,相位寄存器的輸出與相位控制字相加后輸入到正弦查詢表地址中。正弦查詢表包含1個周期正弦波的數字幅度信息,每個地址對應正弦波中0°-360°范圍內的1個相位點。查詢表把輸入的地址相位信息映射成正弦波幅度的數字量信號,去DAC輸出模擬量,相位寄存器每經過228/M個MCLK時鐘后回到初始狀態(tài),相應地正弦查詢表經過一個循環(huán)回到初始位置,這樣就輸出了一個正弦波。輸出正弦波頻率為:

fOUT=M(fMCLK/228) (1)

其中,M為頻率控制字,由外部編程給定,其范圍為0≤M≤228-1。

VDD引腳為AD9833的模擬部分和數字部分供電,供電電壓為2.3V-5.5V。AD9833內部數字電路工作電壓為2.5V,其板上的電壓調節(jié)器可以從VDD產生2.5V穩(wěn)定電壓,注意:若VDD小于等于2.7V,引腳CAP/2.5V應直接連接至VDD。

2.2 功能描述

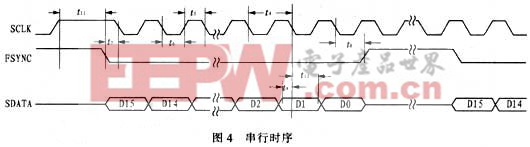

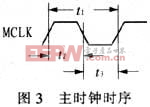

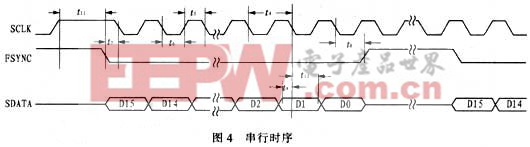

AD9833有3根串行接口線,與SPI、QSPI、MI-CROWIRE和DSP接口標準兼容,在串口時鐘SCLK的作用下,數據是以16位的方式加載到設備上,時序圖如圖3所示,FSYNC引腳是使能引腳,電平觸發(fā)方式,低電平有效。進行串行數據傳輸時,FSYNC引腳必須置低,要注意FSYNC有效到SCLK下降沿的建立時間t7的最小值。FSYNC置低后,在16個SCLK的下降沿數據被送到AD9833的輸入移位寄存器,在第16個SCLK的下降沿FSYNC可以被置高,但要注意在SCLK下降沿到FSYNC上升沿的數據保持時間ts的最小和最大值。當然,也可以在FSYNC為低電平的時候,連續(xù)加載多個16位數據,僅在最后一個數據的第16個SCLK的下降沿的時將FSYNC置高,最后要注意的是,寫數據時SCLK時鐘為高低電平脈沖,但是,在FSYNC剛開始變?yōu)榈蜁r,(即將開始寫數據時),SCLK必須為高電平(注意t11這個參數)。

當AD9833初始化時,為了避免DAC產生虛假輸出,RESET必須置為1(RESET不會復位頻率、相位和控制寄存器),直到配置完畢,需要輸出時才將RESET置為0;RESET為0后的8-9個MCLK時鐘周期可在DAC的輸出端觀察到波形。

AD9833寫入數據到輸出端得到響應,中間有一定的響應時間,每次給頻率或相位寄存器加載新的數據,都會有7-8個MCLK時鐘周期的延時之后,輸出端的波形才會產生改變,有1個MCLK時鐘周期的不確定性,因為數據加載到目的寄存器時,MCLK的上升沿位置不確定。

3 AD9833的引腳功能及時序

AD9833的引腳排列如圖2所示,各個引腳的功能描述見表1。

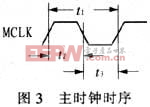

AD9833的時序特性如圖3、圖4和表2所示。

可以通過3個串行接口將數據寫入AD9833,這3個串口的最高工作頻率可以達到40MHz,易于與DSP和各種主流微控制器兼容。AD9833的工作電壓范圍為2.3V-5.5V。

AD9833還具有休眠功能,可使沒被使用的部分休眠,減少該部分的電流損耗,例如,若利用AD9833輸出作為時鐘源,就可以讓DAC休眠,以減小功耗,該電路采用10引腳MSOP型表面貼片封裝,體積很小。

AD9833的主要特點如下:

頻率和相位可數字編程;

工作電壓為3V時,功耗僅為20mW;

輸出頻率范圍為0MHz-12.5MHz;

頻率寄存器為28位(在25MHz的參考時鐘下,精度為0.1Hz);

可選擇正弦波、三角波、方波輸出;

無需外界元件;

3線SPI接口;

溫度范圍為-40℃-+105℃。

2 AD9833的結構及功能

2.1 電路結構

AD9833是一塊完全集成的DDS(Direct Digital Frequency Synthesis)電路,僅需要1個外部參考時鐘、1個低精度電阻器和一個解耦電容器就能產生高達12.5MHz的正弦波。除了產生射頻信號外,該電路還廣泛應外于各種調制解調方案。這些方案全都用在數字領域,采用DSP技術能夠把復雜的調制解調算法簡化,而且很精確。

AD9833的內部電路主要有數控振蕩器(NCO)、頻率和相位調節(jié)器、Sine ROM、數模轉換器(DAC)、電壓調整器,其功能框圖如圖1所示。

AD933的核心是28位的相位累加器,它由加法器和相位寄存器組成,每來1個時鐘,相位寄存器以步長增加,相位寄存器的輸出與相位控制字相加后輸入到正弦查詢表地址中。正弦查詢表包含1個周期正弦波的數字幅度信息,每個地址對應正弦波中0°-360°范圍內的1個相位點。查詢表把輸入的地址相位信息映射成正弦波幅度的數字量信號,去DAC輸出模擬量,相位寄存器每經過228/M個MCLK時鐘后回到初始狀態(tài),相應地正弦查詢表經過一個循環(huán)回到初始位置,這樣就輸出了一個正弦波。輸出正弦波頻率為:

fOUT=M(fMCLK/228) (1)

其中,M為頻率控制字,由外部編程給定,其范圍為0≤M≤228-1。

VDD引腳為AD9833的模擬部分和數字部分供電,供電電壓為2.3V-5.5V。AD9833內部數字電路工作電壓為2.5V,其板上的電壓調節(jié)器可以從VDD產生2.5V穩(wěn)定電壓,注意:若VDD小于等于2.7V,引腳CAP/2.5V應直接連接至VDD。

2.2 功能描述

AD9833有3根串行接口線,與SPI、QSPI、MI-CROWIRE和DSP接口標準兼容,在串口時鐘SCLK的作用下,數據是以16位的方式加載到設備上,時序圖如圖3所示,FSYNC引腳是使能引腳,電平觸發(fā)方式,低電平有效。進行串行數據傳輸時,FSYNC引腳必須置低,要注意FSYNC有效到SCLK下降沿的建立時間t7的最小值。FSYNC置低后,在16個SCLK的下降沿數據被送到AD9833的輸入移位寄存器,在第16個SCLK的下降沿FSYNC可以被置高,但要注意在SCLK下降沿到FSYNC上升沿的數據保持時間ts的最小和最大值。當然,也可以在FSYNC為低電平的時候,連續(xù)加載多個16位數據,僅在最后一個數據的第16個SCLK的下降沿的時將FSYNC置高,最后要注意的是,寫數據時SCLK時鐘為高低電平脈沖,但是,在FSYNC剛開始變?yōu)榈蜁r,(即將開始寫數據時),SCLK必須為高電平(注意t11這個參數)。

當AD9833初始化時,為了避免DAC產生虛假輸出,RESET必須置為1(RESET不會復位頻率、相位和控制寄存器),直到配置完畢,需要輸出時才將RESET置為0;RESET為0后的8-9個MCLK時鐘周期可在DAC的輸出端觀察到波形。

AD9833寫入數據到輸出端得到響應,中間有一定的響應時間,每次給頻率或相位寄存器加載新的數據,都會有7-8個MCLK時鐘周期的延時之后,輸出端的波形才會產生改變,有1個MCLK時鐘周期的不確定性,因為數據加載到目的寄存器時,MCLK的上升沿位置不確定。

3 AD9833的引腳功能及時序

AD9833的引腳排列如圖2所示,各個引腳的功能描述見表1。

AD9833的時序特性如圖3、圖4和表2所示。

評論