基于DSP的繼電保護測試儀信號采集裝置硬件設計

2.5 DSP系統的設計

DSP系統主要由DSP芯片、電源電路、時鐘電路、仿真和測試電路組成。由于TMS320F2812的電源系統既有3.3 V的數字和模擬電源,又有1.8 V的數字電源,電源的安全和可靠是系統運行的根本保證,所以需要將常用的5 V電源轉換成3.3 V和1.8 V電源。本設計選用TI公司的TPS767D318作為電源芯片,該芯片是專門為DSP的應用而設計的,可以提供3.3 V和1.8 V兩路電壓輸出,其中每路輸出均可提供最大為1 A的電流。TPS767D318同時具有電壓監測功能。電源電路的設計如圖6所示。此外,DSP的每個電源和地引腳不能懸空,數字模擬地要分離設計。本文引用地址:http://www.104case.com/article/152016.htm

由于本系統對時序的要求比較敏感,所以本系統的時鐘電路選用3.3 V工作電壓的外部有源晶振。該有源晶振相對無源晶振信號質量更好,而且比較穩定,連接方式相對簡單。通常的用法是:一腳懸空,二腳接地,三腳接輸出,四腳接電壓。

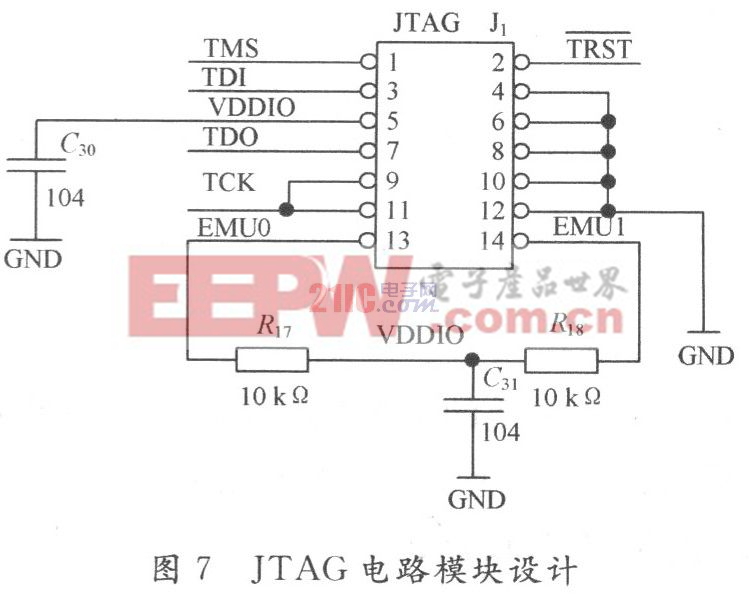

在對DSP系統進行硬件仿真時,可以通過JTAG邊界掃描接口對DSF內部的數據存儲器、程序存儲器和控制寄存器進行在線監控,并能在TMS320F2812的開發環境CCS中把程序下載到DSP芯片進行硬件仿真。JTAG接口的原理圖如圖7所示。

2.6 通訊模塊設計

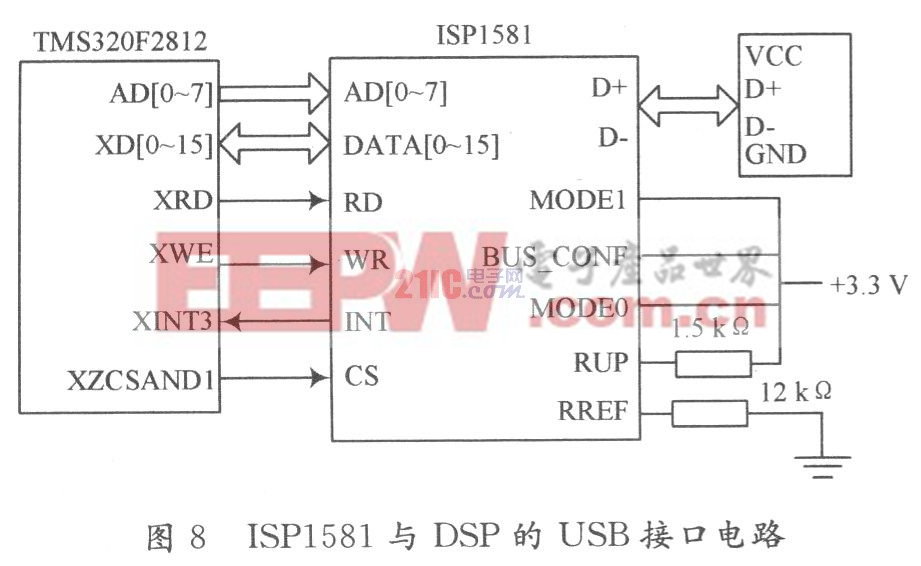

目前,數據采集系統多以ISA,EISA或PCI插卡的形式完成數據的傳輸,這些方式存在著開發調試比較困難、安裝麻煩以及通用性和可移植性差等缺點,而且PC機上的插槽數量、地址、終端資源有限,導致這種方式的可擴展性差。目前,廣泛應用的USB總線接口具有安裝方便、高帶寬、易于擴展等優點,已成為計算機接口的主流。本文選用專用的USB接口芯片來完成DSP與PC機的數據傳輸。USB 2.O芯片選用Philips公司的ISP1581。ISP1581與TMS320F2812的連接電路圖如圖8所示。ISP1581在上電時,通過BUSCONF,MODE0,MODE1對接口進行設置,本設計中BUS CONF通過電阻連接至高電平,ISP1581工作在通用處理器模式,AD[0~7]是8位地址總線,DATA[0~15]是獨立的數據總線。MODE0設為1,因此讀寫選通信號為8051類型。TMS320F2812的XCSOAND1作為ISP1581的片選信號。RREF引腳通過12 kΩ的精密電阻接地,提供精確的鏡像電流。RPU引腳通過1.5 kΩ電阻器上拉。

3 結 語

研制了一種基于DSP技術的繼電保護測試儀信號采集裝置,以便檢定繼電保護測試儀的性能指標是否滿足設計要求。文中重點介紹了數據采集裝置的整體架構、基于DSP的數據采集裝置的硬件組成和電路設計。該數據采集裝置可以精確采集繼電保護測試儀的各項數據,為繼電保護測試儀的檢定裝置奠定了技術基礎。

評論