SoPC系統設計的綜合優化方案

根據器件內3種存儲器的各自特點,結合片內的邏輯資源分布,在片內設計了5個同步FIFO,其中4個長度32位、存儲深度256字的FIFO作為64位PCI傳輸的緩存,另一個長度32位,存儲深度設計為2 048字。M512存儲塊主要用于內部FIFO的設計,在配置片內FIFO時選擇M512存儲塊類型。1個32位長、存儲深度256字的FIFO占用的邏輯資源為30個LUT單元、15個M512存儲塊、134個REG單元。4個這樣的FIFO占用60個M512存儲塊、120個LUT單元。536個REG單元。而1個32位長、2 048字存儲深度的FIFO占用的邏輯資源為114個M512存儲塊、63個LUT單元、128個REG單元。這樣,系統設計中的FIFO總共占用174個M512存儲塊,相比表1中EP2S60器件329個M512存儲塊,占用率為52.9%,完全可以在片內設計實現。

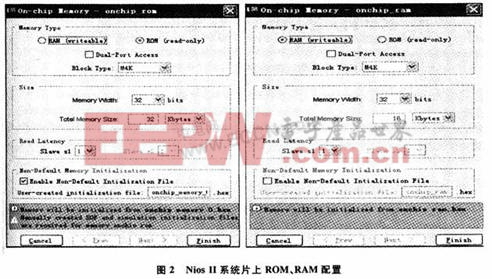

類似計算機系統,軟CPU Nios II系統也需要配置片上的ROM和片上RAM,如圖2所示。片上ROM設計存儲器類型為M4K,數據寬度32位,深度為32 KB,讀延遲1。片上RAM存儲器類型同樣為M4K,數據寬度32位,深度設計為16 KB,讀延遲1。

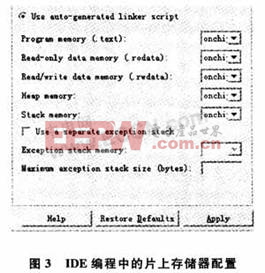

片上ROM主要用于上電后程序從外部存儲器加載完成后的程序存儲,是IDE主程序開始執行的地方。在Nios II自動分配的地址中,一般起始地址為0x00000000,目的地址為設計ROM容量的大小。片上RAM主要作為程序運行的緩存和程序異常時的暫存,相當于計算機中的內存。在IDE編程設置中,要對片上ROM和片上RAM的使用進行具體的設置,如圖3所示。

對程序存儲器和只讀數據存儲器,設置為使用片上ROM。對讀寫數據存儲器、堆存儲器和堆棧存儲器,設置使用片上RAM存儲器。這樣,可以作到有效的存儲器配置。

2.4 針對NiOS II系統的優化

SOPC系統在沒有添加Nios II系統時,較容易實現比較高的頻率,在加入Nios II系統后,系統設計頻率有較明顯的下降。因此在帶Nios II的系統中,對Nios II的優化設計是制約整個SOPC系統時序的一個瓶頸。

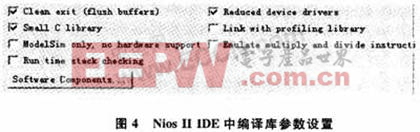

另一方面,在Nios II系統中,多是應用已經設計好的軟核CPU和外接器件IP核,在設計時已經進行過優化并且已經封裝集成,進一步優化的難度很大,因此優化主要放在自行開發設計的IP核和軟件的參數配置以及設計NiosII系統時應當遵循的一些原則上。在Nios II IDE編程環境中,如圖4所示,選擇最大優化,在編譯器參數設置中選擇小的C編譯庫和減少設備驅動,這樣經優化后可以縮減硬件代碼,減少器件資源占用。

參考文獻[7]中探討了Nios II系統的優化途徑。文中歸納系統優化有如下方法:

①運算應采用定點運算。經過測試,浮點加法和乘法運算消耗的時間為定點運算的5~6倍,如果需要浮點運算,也應該采用自定義指令的方式來實現。

②采用C語言和匯編語言混合編程。對計算量大的多次調用的程序模塊采用匯編語言,對主干流程語言采用C語言,這樣可以照顧到程序的可讀性,效率也較高,同時縮減程序占用資源量。

③使用用戶自定義指令。將一些復雜的算法由軟件轉而交由硬件來實現,可以獲得較高的效率提升。

④使用硬件加速提高軟件性能。通過添加外部協處理器來加速數據功能。

⑤多處理器系統。使用兩個或多個處理器來提高系統的數據處理能力。

通過上面分析,進行系統優化似乎是一個矛盾的過程:有時需要優化以縮減代碼量并減少資源占用,有時又通過增加邏輯和添加處理模塊來提升數據處理能力。實際上,評價一個系統設計的好壞,除了需要實現基本的功能外,還要看使用邏輯資源和性能的綜合比較,以更好地利用處理器,達到最好的性能。

3實驗結論

在系統設計中,應用文中分析的綜合優化設計方法,系統最高頻率有了較大提升,從最初的88.24 MHz,優化至目前的111.73 MHz。由于在Quartus II編譯器參數沒置中,要求最高時鐘設置為132 MHz,因此優化后最高時鐘報告以紅色顯示,表示沒有達到預先設置的132 MHz時鐘要求。相比于優化前,系統最高頻率提高了26.62%,可見采取的綜合優化設計措施比較有效。對于EP2S60器件,在沒有添加Nios II系統時,可以較容易達到200~300 MHz的最高時鐘頻率,加入Nios II經過優化處理,最高時鐘頻率目前只實現111.73 MHz,應該還有進一步優化空間。可以考慮對關鍵路徑進行手工連線,采用DSE算法和邏輯鎖定技術進行進一步的優化,從而提高系統最高頻率.

評論