SOC中多片嵌入式SRAM的DFT實現方法

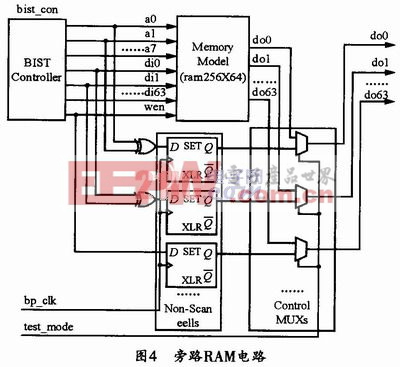

若測試覆蓋率較低,首先應分析DRC(design rule constraint)Violations,并盡量消除DRCViolations。再分析AU(ATPG untestable)報告,減少AU的數量。按照模塊層次來報告測試覆蓋率時,應找到覆蓋率低的模塊重點分析。該項目的AU報告中和RAM有關的部分占了很大一部分。RAM自測試模塊的測試覆蓋率只有6%。分析工具把RAM當做black box,由于這些SRAM的數據位很寬,故SRAM數據端口不可控和不可測的邏輯(稱為陰影邏輯)更多,芯片的測試覆蓋率也更低。給RAM加旁路(bypass)邏輯,測試模式下將輸入和輸出連起來,可使原來不可控和不可觀測的邏輯變化反映到掃描鏈上,使之變得間接可控和可觀測,從而提高整個芯片的測試覆蓋率。RAM的輸入比輸出多,故可用XOR連接。對于XOR/XNOR門,為了將故障響應從它的一個輸入傳播到它的輸出,可根據方便程度設置所有其他的輸入為0或1。而對于AND/NAND門,為了將系統的故障響應從它的一個輸入傳播到它的輸出,則必須通過將其他輸入設置為l來實現,其中“l”對于AND/NAND門是一個非控制值。同理,“0”對于OR/NOR門也是一個非控制值。圖4所示是旁路RAM的電路示意圖。圖中,多路選擇器由test_mode信號控制,與RAM的輸入輸出連接的邏輯可測,RAM模塊的測試覆蓋率可提高到98.3%,相應的整個芯片的測試覆蓋率提高了4個百分點。本文引用地址:http://www.104case.com/article/151464.htm

由此可見,MBIST結構可直接實例化地用在數字設計部分。該系統的功能邏輯部分含有萬余寄存器,為了提高測試覆蓋率添,加幾個寄存器及很少組合邏輯作為測試點后,即可將測試覆蓋率提高且不會增加太大的面積開銷,因而這種方法是很有效率的。如果前期設計時就能考慮這種測試結構,DFT設計過程中就會減少反復,減少測試設計周期。

5 結束語

本文基于一個實際項目,分別用常用的并行與串行兩種方式來實現MBIST的構架,并對其開銷進行了定量與定性討論,結果是對于不同的設計,應當靈活構建測試結構以達到設計目的。對于在嵌入式存儲器數量較少,位寬較小的情況下,MBIST對掃描測試覆蓋率的影響并不明顯,易被人們忽視,一旦這種影響顯著發生,比較高效的方法是插入旁路電路,這樣,在提高覆蓋率的同時也不會增加太大的面積開銷。可見,對于一個嵌入多片SRAM的SOC進行DFT設計時。應從多維度靈活處理,折中考慮。

評論