嵌入式單總線控制器設計

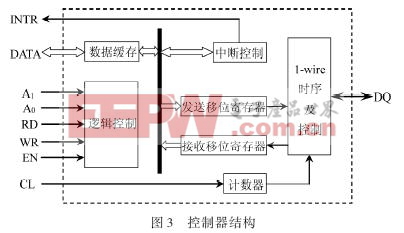

2.1 控制器結構

控制器結構如圖3所示,控制器由4部分組成,即邏輯控制、單總線時序控制、數據緩存和計數器。邏輯控制部分用于實現與CPU的通信,D0~D7為8位雙向數據線,EN為啟動信號,下降沿有效。A1、A0為地址信號,其組合決定控制器的工作狀態。A1A0=00,控制器對DS1820執行復位操作;A1A0=01,控制器執行寫入操作;A1A0=10,控制器執行讀出操作。控制器由外部提供200 kHz的時鐘信號CLK,產生5 μs的計數周期,控制器以5 μs為一個時間片形成DS1820的讀寫時序。計數器的計數輸出值控制讀寫周期。單總線時序控制部分的主要功能是產生單總線的讀寫時序,并向DS1820輸出控制命令,讀出DS1820測得的數字溫度值及其他輸出信息。

2.2 讀寫時序的實現

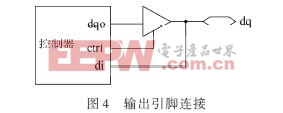

DS1820要求引腳驅動必須是漏極開路引腳,控制器用三態門與DS1820連接,如圖4所示。其中ctrl為三態門控制信號,當ctrl=0時輸出信號,ctrl=1時輸入信號。控制器采用5 μs作為基本計時單位,可以保證DS1820時序關系有一定的余地。

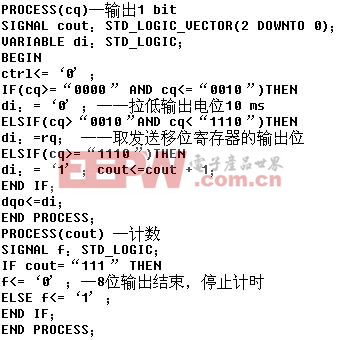

寫字節部分VHDL代碼:

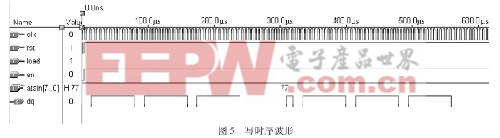

3 仿真波形

控制器的VHDL程序在MAX+plusII平臺編譯通過,并獲得了正確的復位、讀、寫時序。圖5為寫時序波形,寫入77H字節。每次寫入新的bit前,控制器將總線電平拉底10 μs。

基于VHDL的嵌入式DS1820控制器,具有轉換速度快、精度高、通用性好等優點。同時,嵌入軟核的FPGA可以分擔許多微處理器的工作,降低系統對CPU實時性的要求,也降低了軟件開發的難度。本文雖然是針對DS1820設計的控制器,但由于單總線通信協議的通用性,也可以用于其他單總線器件。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論