TURBO51嵌入式微處理器功能驗證

TURBO51的FPGA 驗證的前提是設計已經過了關鍵點的形式驗證, 完成了塊覆蓋率為100% 的RTL仿真及代碼檢查且錯誤已收斂完畢, 故對FPGA驗證的首要目的是通過運行和真實應用環境完全相同的完整目標應用系統驗證兩步的錯誤估計是否正確并配合其他SOC 模塊作SOC 協同驗證。因為對有的仿真做起來不方便的系統驗證在FPGA 平臺上很方便驗證。在TURBO51的FPGA 驗證中, 充分利用了FPGA 上的剩余資源, 用于實時定位與監測TURBO51的FPGA 實現版每個時鐘的狀態及其運行狀態, 這其實已使原本認為FPGA 上難于定位錯誤的缺陷大為改觀, 在真實環境下運行系統提供了非常接近RTL仿真的調試能力的觀測窗口。這里依然首先選用了指令提交地址和指令取指地址,累加器, B 寄存器, 程序狀態字PSW, 重定序緩沖狀態, 例外處理標識, 寫回總線,提交總線位為主要觀察點, 顯示每個時鐘的狀態, 將它們協同SOC 其它模塊的輸出, 示波器觀測輸出波形結果一起形成FPGA 驗證結果。TURBO51在FPGA 驗證時工作在60MH z, 除運行全部手工編寫的用于模擬仿真的測試程序外, 還成功連續兩百小時運行全部現有量產的基于RTOS商用系統及其極限條件, 沒有發現嚴重錯誤。通過對寄存器值的實時監測發現十處以內的外設非致命錯, 比如GPIO 與外設輸入輸出復用。

當然, 每改一次RTL或監視寄存器都需要重新進行FPGA 燒寫文件的生成, TURBO51耗時近兩小時, 故它仍然不可能取代仿真。完成FPGA 驗證后做準備流片的工廠提供的工藝標準單元庫綜合及靜態時序分析, 交出網表做后端布局布線, 完成后再用帶門延時的后端門級網表進行門級仿真,最后編寫樣片基臺測試程序。

6 驗證結果分析

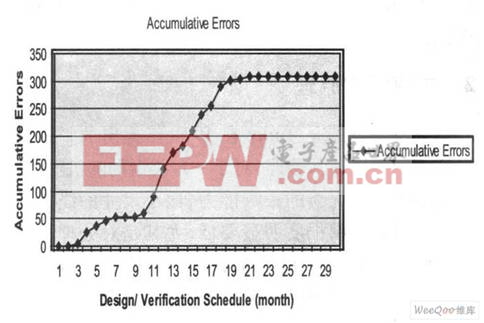

由于最初在制定實現的方法和制定驗證計劃時是同步進行的, 致使整個設計階段的錯誤累積。在TURBO51的設計和驗證中, 首先用形式驗證將最高風險的存貯訪問, 高速緩存, 分支預測, 動態執行, 例外處理中的最高風險組合進行完備證明,使錯誤得以排除。在此后的驗證中, 凡經形式驗證正確的部分再未出現過異常, 如圖1所示。

圖1 錯誤時間累計統計。

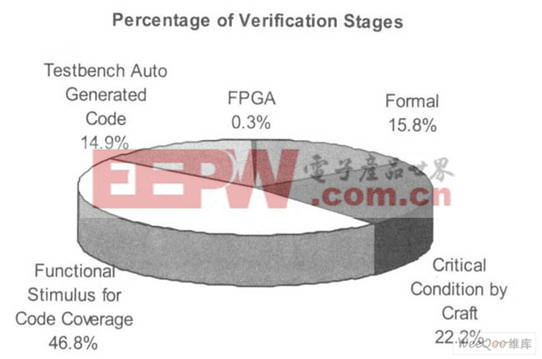

這樣使得全部的高風險錯誤在RTL仿真的中期已經全部排除并且大多數都由手工編寫的測試激勵完成。由于8051指令集指令死角空間相對較小,手工編寫可行。其中大部分RTL 仿真發現的錯是IO設備錯誤與處理器指令執行部分無關。如圖2所示, 錯誤99. 7% 百分比在FPGA 驗證前已收斂,故可認定前面工作扎實有效。假如一個設計如果在FPGA 驗證階段錯誤還未能收斂完, 還能發現大量新增錯誤尤其是嚴重錯誤的話, 這說明仿真及行為模型描述與驗證計劃都存在嚴重問題,應退回去重走一遍, 否則流片風險較大。

圖2 不同驗證階段發現的錯誤分布統計。

7 總結和未來工作

TURBO51嵌入式微處理器使用了上述多種驗證方法使得越嚴重的錯誤得到了越早的收斂, 加上高的RTL代碼覆蓋率及長時間在FPGA 上成功運行了全部目標應用程序及所有仿真測試程序, 表明設計正確且兼容性完備, 使TURBO51嵌入式微處理器順利采用富士通微電子(日本) 90nmCMOS 工藝一次流片成功。但另一方面, 可配置約束的自動隨機指令序列已在更復雜的處理器驗證中越來越廣泛地采用, TURBO51的驗證中在這一方面目前還處于初級階段, 這將是以后的主要改進方向。

評論