現場可編程門陣列的結構與設計

摘要:現場可編程門陣列(FPGA——Field Programmable Gate Array)是上世紀80年代末發展起來的新型大規模集成邏輯器件。它采用高級計算機輔助設計技術進行器件的開發與設計,其優越性大大超過普通TTL集成門。重點介紹了FPGA的基本組成原理及設計方法。

本文引用地址:http://www.104case.com/article/150946.htm

1 引言

FPGA是上世紀80年代末開始使用的大規模可編程數字集成電路器件。它充分利用計算機輔助設計技術進行器件的開發與應用。用戶借助于計算機不僅能自行設計專用集成電路芯片,還可在計算機上進行功能仿真和實時仿真,及時發現問題,調整電路,改進設計方案。這樣,設計者不必動手搭接電路、調試驗證,只須在計算機上操作很短的時間,即可設計出與實際系統相差無幾的理想電路。而且,FPGA器件采用標準化結構,體積小、集成度高、功耗低、速度快,可無限次反復編程,因此,成為科研產品開發及其小型化的首選器件,其應用極為廣泛。

2 FPGA的基本組成原理

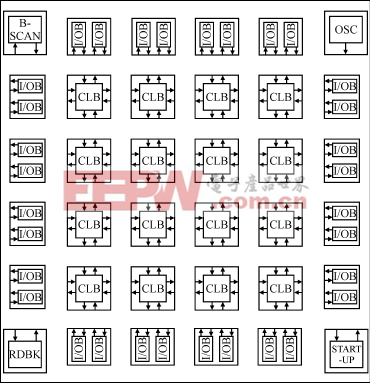

FPGA的基本組成與生產廠家有關,不同廠家的器件其結構、工藝技術和編程方法各不相同。目前國內廣泛使用Xilinx公司生產的FPGA器件。XilinxFPGA采用邏輯單元陣列(Logic Cell Array—簡稱LCA)結構,其示意圖如圖1所示。

圖1 Xilinx公司FPGA結構圖

由圖1可知,XilinxFPGA由3個可編程基本單元陣列組成:輸入/輸出塊(I/OBlock—簡稱I/OB)陣列,可配置邏輯塊(Configurable LogicB lock—簡稱CLB)陣列及可編程互連網絡(Programmable Interconnect—簡稱PI)。其中輸入/輸出塊排列在芯片周圍,它是可配置邏輯塊與外部引腳的接口。可配置邏輯塊是FPGA的核心,它以矩陣形式排列在芯片中心。每個CLB均可實現一個邏輯功能小單元。各CLB之間通過互連網絡編程連接,以實現復雜的邏輯功能。

3 FPGA的開發過程

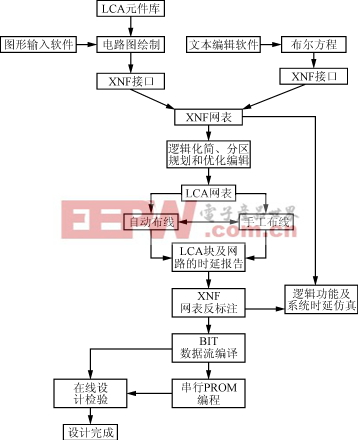

FPGA的開發過程依賴于它的軟件開發系統,其設計流程如圖2所示。

由圖2可知,FPGA的基本設計流程分為3部分:設計輸入,設計實現及設計驗證。

圖2FPGA的基本設計流程

評論