實現8位微控制器升級至32位的關鍵

現今基于嵌入式微控制器 (MCU) 的應用對功能的要求不斷增多,例如,電機控制必須具有更高的能源效率;以往獨立的應用也必須聯網。在這種情況下,對微控制器的性能和存儲容量的要求也大為提高。對一些應用而言,解決的方法就是從8位或16位MCU升級至32位。這樣一來,雖然性能得以提高,但也可能導致單元成本、系統復雜性以及軟件開發成本的增加。本文將討論如何通過系統集成將8位功能加入至32位系統中,以及提供功能強大的低成本開發工具,從而加快這種升級過程。

本文引用地址:http://www.104case.com/article/150823.htm通過提升制造技術可以降低單元成本。不過,除非32位MCU具備和8位或16位系統相若的系統集成度,否則這些優點都將因為加入外部器件的成本而一筆勾銷。高性能系統獨有的高速緩存等往往令系統變得復雜。但是對那些正在升級至 32 位系統的典型實時控制應用而言,這些并不是必需的功能。雖然,把現有代碼移植到新一代更高性能微控制器的成本是無法省去的,但為了減少整體所需的工作量,可以通過開發工具的設計來推動這種升級過程。

市場趨勢:轉向32位MCU

根據Gartner Dataquest公司統計,在過去10年間,32位微控制器在MCU市場的營業額從零開始增長到了近25%,目前的增長率高于8位或16位系統。而且,隨著眾多配備了針對特定市場領域,如汽車市場等的功能集的器件不斷涌現,MCU 市場正在逐步分化。 從8位和16位MCU升級至 32位架構的重點是深度嵌入式實時控制應用。

此外,目前產業界還出現了一個明顯趨勢,就是ARM RISC處理器正逐漸成為32位MCU的行業標準,一如當初8051架構是8位系統的標準。目前,ARM 在32位嵌入式RISC MCU市場的占有率達 75%,截至2005年1月,ARM各合作伙伴已付運超過25億片的的ARM 內核的MCU。

成本:技術和整合度的考慮

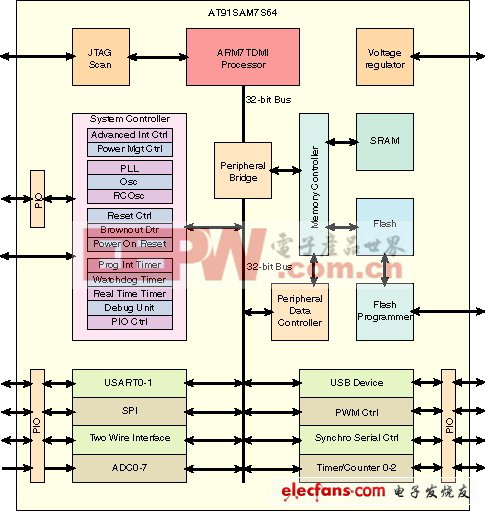

采用當前0.18μm的工藝技術,生產一塊包含有一個32位RISC處理器、標準外圍設備和一個小容量閃存的單芯片成本并不昂貴,但對于8位應用而言,單憑此尚不足夠。從8位微控制器升級的應用需要有更高水平的系統集成度 (見圖1),來滿足整體的系統成本預算。而且,這種整合度必須讓32位系統具有8位片上系統的基本功能。

32位器件必須采用單電源工作;集成大電流驅動 I/O 和收發器;控制系統上電;通過低成本晶振生成系統時鐘;而且其 I/O上應具有可編程上拉電阻 (pull-up)。此外,32位器件還應確保在任何環境下應用的行為都可以預測,這需要一個節電檢測器 (brown-out detector)、一個可編程監視器,以及一個集成RC振蕩器,而毋需高速緩存和閃存加密位 (lock bit)。

從8位升級至 32位系統時的性能要求

嵌入式閃存的訪問時間

基于8位微控制器的應用一般是以控制為主導 (control-driven) 的,要求對外部事件的確定過程式 (deterministic) 響應和可預測的響應時間。然而,用來加快對緩慢非易失性儲存媒介之存取速度的高速緩存卻不是決定性的,因此對于那些對時間要求嚴格的應用來說是不可接受的。提高實時性能又不增加成本的惟一方法,就是加快對嵌入式閃存的存取速度。

目前產業界的0.18μm工藝技術能在30MHz的ARM微控制器上進行單周期內訪問,原始性能可達27MIPS,遠高于現有的一般 8位微控制器。

提高中斷處理能力

實時控制應用一般是采用中斷驅動,利用多個中斷源和規定每一中斷時間內所需的響應來進行。基本的ARM架構有一個弱點,就是它的中斷處理機制很簡陋,沒有中斷優先所需的硬件裝置。這時便需要一種裝置來增強中斷能力,如圖2所示。它提供一組帶有 8 個優先級別之可獨立屏蔽的向量式中斷源。永久存儲在SRAM中的基本中斷處理程序負責分配中斷的優先級級別,然后執行一條指令,利用中斷號 (每一中斷源均獲發一個獨有編號) 作為偏移量 (offset),把用于所需中斷服務程序的向量直接裝載入程序計數器 (Program Counter)。這種簡單有效的機制能夠確保在最少數目的指令周期內,把控制傳送到所需的中斷服務程序中。

評論