基于 DSP-dMAX 的嵌入式 FIFO 數據傳輸系統設計

系統軟件設計

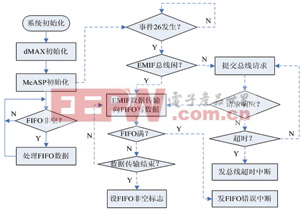

系統軟件設計主要包括McASP的初始化、dMAX的初始化、FIFO的初始化、中斷使能等。系統主程序只需要等待中斷進行相應的處理,主要的數據傳輸工作都是dMAX按照軟件配置自動完成,不需要CPU參與。圖4是實現由外設寫FIFO,DSP讀取FIFO數據的流程。圖中虛線部分表示由dMAX獨立完成的工作,實線部分表示由CPU完成的工作。兩者之間通過內部中斷方式實現狀態的交流。

圖4 系統軟件流程

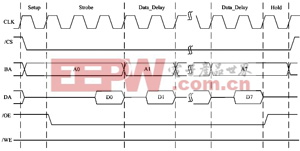

為了提高FIFO的讀寫速率,一般采用突發方式進行讀寫。突發方式的讀時序如圖5所示。寫時序和讀時序類似。突發方式一次最多只能讀寫8個數據,也可以一次突發讀寫4個或者2個數據。突發讀寫時數據的建立和保持時間最少可以設置成1個時鐘周期,如圖中所示。但為了通信可靠,一般采用2個時鐘周期。突發方式最大的節省時間是連續的其他數據將不再需要建立和保持周期,而是直接進行讀寫,一般只需要兩個時鐘周期就可以完成一個數據的讀寫。最快情況下,突發讀寫8個數據只需要20個時鐘周期,讀寫速率達到53.2M×32b/s,滿足大部分設備的要求。

圖5 突發讀時序圖

總結

dMAX的特有結構使得其可以實現嵌入式FIFO。本文介紹了基于C6727B的dMAX的基本結構以及基于dMAX的嵌入式FIFO軟硬件設計,設置通用GPIO引腳作為中斷,為了加快FIFO的傳輸速率,使用突發讀寫方式進行數據傳輸。嵌入式FIFO的實現,使得DSP和外部設備的通信更加方便和快捷,而且不需要CPU的參與,減輕了CPU的負擔,CPU可以專注于復雜的算法處理。

評論