CPLD在TMS320F2812系統中的應用

1 引言

本文引用地址:http://www.104case.com/article/150593.htm TMS320F2812是美國德州儀器公司推出的C2000 家族中最新一代產品。先進的內部和外設結構使得該處理器主要用于大存儲設備管理、高性能的控制場合。在F2812構成的應用系統中,需要設計一些邏輯控制電路來保證系統正常有序地工作。這里,我們采用CPLD 來設計外圍電路的譯碼及邏輯控制,使DSP 系統達到小型化、集成化和高可靠性。

2 CPLD在TMS320F2812系統中的應用

2.1 TMS320F2812介紹

TMS320F2812 數字信號處理器是在F24X的基礎上開發的高性能定點芯片。能夠運行24x 開發的代碼程序,并且F2812 采用32bit 操作大大提高了處理能力。它的主要特點如下:

采用高性能的靜態CMOS 技術,主頻可以工作在150 MHZ(時鐘周期可達6.67ns);

高性能的 32 位中央處理器,可以進行16 位X16 位以及32 位X32 位的乘且累加操作;

片內大容量存儲器,128 K×16 bits 的Flash 和18 K×16 bits 的數據/程序存儲器;

高速外設接口,最多可擴展1.5 M×16 bit 存儲器;

3 個32-bit CPU 定時器,其中CPU 定時器1 和CPU 定時器2 被保留用作實時操作系統OS。CPU 定時器0 可供用戶使用,作為獨立的,全局性的定時中斷控制;

具有 12-bit 的 ADC 流水線變換時間最小60 ns,單變換200 ns;可選擇兩個時間管理器觸發功能;

改進的 eCAN 2.0B 接口模塊;

多種串行通信接口(2 個UART、1 個SPI 及1 個MCBSP);

高性能低功耗,采用1.8V 內核電壓和3.3V外圍接口電壓;

2.2 硬件結構介紹

我們采用 Alter 公司的EPM7064S 芯片來完成內部邏輯管理及與總線接口工作。該芯片采用快閃存儲技術(FastFLASH),功耗較低。宏單元數達到64 個,完全滿足設計的邏輯要求。引腳到引腳的延時為4ns,計數器頻率可達151MHZ。其輸出電壓為3.3V 或5V,可以通過設置VCCIO 引腳來選擇不同的輸出電壓。I/O 引腳可接受5V、3.3V 和2.5V 的混合電壓輸入,在多電源混合系統中,這一特性非常有用,可以節省大量的電平轉換器。

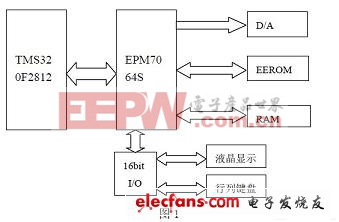

TMS320F2812 應用系統需要外擴一些必要的電路,包括支持內部程序運行的RAM 和EEROM,以及D/A 轉換電路等,其系統結構框圖如圖1 所示:

2.2.1 數模轉換器的應用

在 TMS320F2812 中,片外擴展是通過TMS320F2812 中的外設接口XINTF 來實現的。

它類似于C240X 的外部接口,但也做了改進:

(1)在C240X中,程序存儲空間、數據存儲空間和I/O 空間映射在相同的地址(0000~FFFF),對它們的訪問通過控制線( DS , PS , IS )來區分;而在F2812 中,外部存儲器接口分成了5個固定的存儲映像區域,可尋址1MB 的片外存儲器空間,具有獨立的地址,沒有了控制線( DS , PS , IS )。

(2) 每個 F2812 的XINTF 區都有一個片選信號。其中,有的區域的片選信號在內部是“與”在一起的,組成了一個共享的芯片選擇,比如XZCS0 和XZCS1共享一個片選信號XZCS0AND1,XZCS6和XZCS7共享一個片選信號XZCS6AND7。在這種方式下,同一個存儲器可被連到兩個區或者我們可以用外部譯碼邏輯來區分這兩個區。

(3)5 個固定的存儲映像區域的每一個區還可以分別指定等待狀態數,選通信號的建立時間,激活時間和保持時間。這些特征使得接口與外部存儲器及外設脫離了聯系,可以靈活獨立地進行外部擴展。在本次設計中,除了液晶除了液晶顯示模塊和鍵盤外,所有的外擴寄存器和存儲器全部映射在XINTFZONE 2(0x080000~0x0FFFFF)譯碼的空間內。我們使用了DAC7625 作為數模轉換芯片,該芯片為4 通道12 位雙緩沖的DAC 芯片,工作電壓可以是+5V 或-5V~+5V 的模擬電壓。

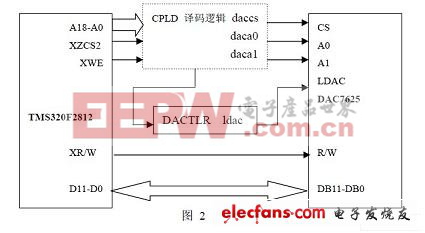

輸出電壓是0~3.3V 的直流電壓。功能框圖如圖2 所示:

其中,DAC7625 芯片中LDAC 引腳為載入DAC 引腳,當為低電平時,所有寄存器為透明,保持寄存器里的數據送到轉換器輸出通道;A1、A0 引腳為寄存器選擇引腳,CPLD根據地址總線譯碼選通不同的A1、A0 組合,從而將1 ~ 4 通道的保持寄存器映射到0xC0000~0xC0003 的地址空間。此外,我們還設計了傳送寄存器(DACTLR),映射地址為0xC0004,這個寄存器的所有數據位都無效,既不可讀也不可寫。對這個寄存器執行任何讀或寫操作都會產生一個內部信號,將LDAC 引腳置為低電平,啟動轉換器工作。其中,整個譯碼邏輯都是由CPLD 芯片完成。下面介紹譯碼邏輯的部分VHDL 語言描述:

評論