基于CPLD和嵌入式系統的LED點陣顯示

2 軟件設計和編寫

2.1 主控電路CPLD芯片設計與調試

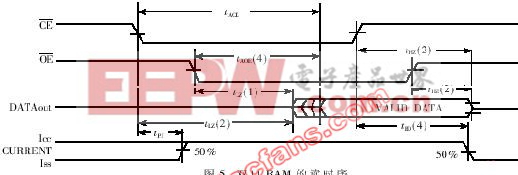

主控電路的功能是讀取雙口RAM中的數據并通過譯碼邏輯電路將數據顯示在LED點陣顯示屏的特定位置上。因為只用到單片機的一部分功能,所以使用CPLD芯片將MCU中的總線讀控制器及其外圍譯碼邏輯電路集成在一起。如若采用傳統方案,就必須采用多片芯片;而使用CPLD后,只用一片芯片就可以實現所要的功能。總線讀控制器是產生時序的電路,需根據內存的讀時序進行設計,只有保證正確的時序才能讀出數據。雙口RAM的讀寫時序和普通RAM的讀寫時序基本相同,如圖5所示。 CE(芯片使能)是片選信號,在片選信號從高變低之前必須輸出地址信號給雙口RAM,然后再用讀信號去控制OE(輸出使能)端,在OE信號由高變低后,數據總線上的數據有效,即可控制讀出數據并譯碼輸出。

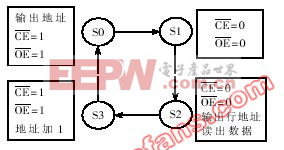

復雜的時序電路用硬件描述語言描述,一般是用有限狀態機來描述。有限狀態機是時序電路通用模型,任何時序電路都可以表示成有限狀態機。從本質上講,有限狀態機是由寄存器與組合邏輯構成的時序電路,各個狀態之間的轉移總是在時鐘的觸發下進行的。針對圖5所示的讀時序,可列出如圖6所示的各種狀態的轉換圖。用Verilog HDL語言描述時可用帶有always語句的case語句建模,狀態信息存儲在寄存器中,case語句的多個分支包含每個狀態的行為。在這里將讀時序分為S0、S1、S2、S3四個狀態,其工作方式如下:

步驟S0在RAM的片選CE 使能之前輸出地址;

步驟S1選中RAM,輸出讀信號;

步驟S2行計數器輸出,讀出RAM的數據并反相輸出;

步驟S3片選禁止,讀禁止,地址計數器加1。

譯碼輸出邏輯電路主要是提取地址計數器的計數輸出。在某個狀態下,行地址計數器輸出低5位數據,位譯碼輸出高4位數據并譯碼輸出16個位選信號。

時序電路中一般留有復位信號,當復位端為1時,地址計數器復零,地址輸出復零,片選。讀控制信號置1,使狀態機回到狀態S0。

2.2 行譯碼CPLD芯片設計

行譯碼器的功能較主控電路來講相對簡單,它是將主控電路的行計數器輸出的6位二進制數據譯成32行的行選通信號,去控制行驅動管驅動行輸出。這是一個純組合邏輯電路,使用Verilog HDL 語言描述的always語句和case 多分支語句即可實現此功能。

2.3 單片機的C程序設計

在本系統中,單片機的功能主要是負責通信與數據處理。通信即通過串口接收來自PC機的數據并存儲在EEPROM中;數據處理即從EEPROM中取出數據并根據要顯示的效果進行軟件處理,再存放在雙口RAM中。在本系統中,因單片機及外圍電路只負責通信和數據處理,對實時性要求不高,因此用前后臺系統進行軟件設計就能達到要求。本系統采用嵌入式操作系統RTX51TNY(KEIL C平臺自帶的免費的微實時內核)。軟件主要由PROCESS.C和SERIAL.C兩個檔組成。PROCESS.C包含三個任務:任務0,初始化;任務1,靜態顯示;任務2,左移顯示。 SERIAL.C是串口中斷程序$靜態顯示的算法較簡單,只要將EEPROM中的字模數據存放到雙口RAM中的特定位置即可。左移顯示則需要將字模數據每個字節左移,然后存放在雙口RAM的特定位置。

評論