PC104總線與DSP數據通信接口設計

其中有效表示數據總線的高8位有效,SA0有效表示數據總線的低8位有效,作為譯碼信號的一部分,對于單片16位數據線的集成電路,實際上也可以不連接,用SA0和高端地址線譯碼產生選片信號。AEN信號有效表示計算機在和某個設備進行DMA傳送,其他的設備發現AEN信號有效,就不要響應尋址信號。因此在CPLD內部邏輯里設置當AEN信號有效時,將進入CPLD的地址信號線置為高阻態。

本文引用地址:http://www.104case.com/article/150406.htm![]()

是存儲器讀寫信號,是用于1 M以外地址空間的讀寫信號,當這兩個信號之一有效且尋址到1 M內的地址,將分別使1 M以內地址的讀寫

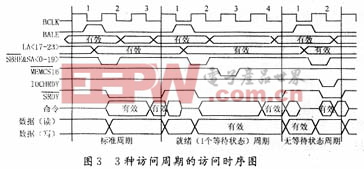

一起控制總線周期的長短。有3種存儲器訪問周期:標準周期,就緒周期,無等待狀態周期。訪問時序如圖3所示。

?

在設計的時候考慮到信號在CPLD里的延時,如果標準周期對于訪問的時間長度不夠,可以采 用有1個等待狀態的就緒周期,而這只需要修改CPLD的設計并重新下載到CPLD即可,由此可 見用CPLD作為控制芯片的優點。

4結語

本文說明的這種PC104總線與DSP的數據通訊接口設計,也可以作為采用其他計算機總線與DS P進行16位數據通訊接口設計的參考。

評論