ISA總線實(shí)現(xiàn)多路同步DDS信號(hào)源設(shè)計(jì)

直接數(shù)字式頻率合成器以其極高的頻率分辨率、極短的頻率轉(zhuǎn)換時(shí)間、相位精確可調(diào)、設(shè)備結(jié)構(gòu)簡(jiǎn)單、易集成、體積小及成本低等優(yōu)點(diǎn),在高分辨雷達(dá)系統(tǒng)、寬帶擴(kuò)頻通信系統(tǒng)以及現(xiàn)代測(cè)控系統(tǒng)中得到廣泛的應(yīng)用。為了便于信息的采集、處理和操作控制,常常要求信號(hào)源基于PC機(jī)平臺(tái)設(shè)計(jì)。PC機(jī)內(nèi)部有兩種常用的總線,即PCI總線和ISA總線。ISA總線接口關(guān)系簡(jiǎn)單.操作控制方便,能夠滿足系統(tǒng)要求,是比較理想的DDS與計(jì)算機(jī)的接口總線。隨著電子系統(tǒng)復(fù)雜性的不斷增加,單路DDS已經(jīng)不能夠滿足系統(tǒng)需求,多路DDS系統(tǒng)的設(shè)計(jì)開始成為研究的熱點(diǎn)。

本文引用地址:http://www.104case.com/article/150381.htm1 系統(tǒng)工作原理

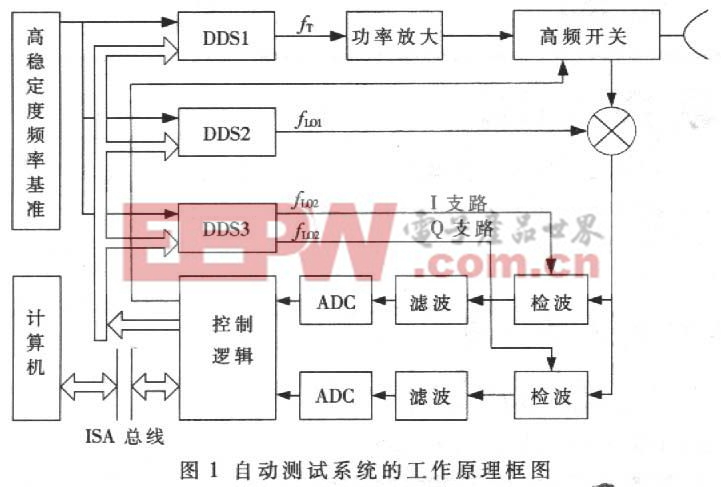

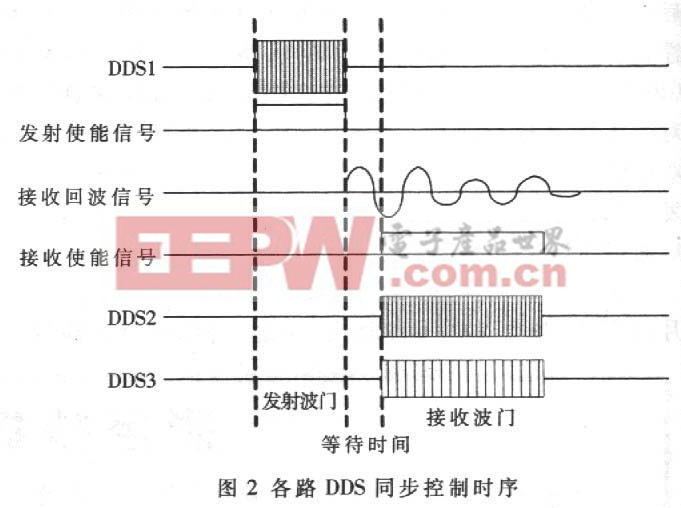

圖1是某自動(dòng)測(cè)試系統(tǒng)的工作原理框圖。圖中的高穩(wěn)定度頻率基準(zhǔn)為整個(gè)系統(tǒng)提供頻率為50MHz的參考時(shí)鐘。系統(tǒng)的控制命令由計(jì)算機(jī)發(fā)出,經(jīng)過ISA總線傳輸,送到FPGA進(jìn)行緩存、譯碼,同步控制三路DDS產(chǎn)生需要的信號(hào)。其中,DDS1的輸出信號(hào)為初始相位可變,脈沖寬度、脈沖周期、脈沖個(gè)數(shù)等由計(jì)算機(jī)編程設(shè)定的射頻脈沖序列。脈沖的載波頻率在fT=2lMHz附近可調(diào)。該射頻脈沖經(jīng)過功率放大、低通濾波后,在高頻開關(guān)的控制下發(fā)射出去。接收到的反射回波由高頻開關(guān)選通,與DDS2產(chǎn)生的20MHz第一本振fLO1混頻,得到頻率為1MHz的中頻脈沖調(diào)制正弦信號(hào)。該中頻信號(hào)再分成兩路,分別與DDS3輸出的頻率為1MHz二本振fLO2的1支路和Q支路兩路脈沖調(diào)制正交信號(hào)進(jìn)行相位檢波,得到的信號(hào)經(jīng)低通濾波、模數(shù)轉(zhuǎn)換,送到計(jì)算機(jī)進(jìn)行數(shù)據(jù)處理。為保證收發(fā)信號(hào)有效可靠地隔離,在發(fā)射波門和接收波門之間插入等待時(shí)間。各路信號(hào)之間的關(guān)系如圖2所示。為簡(jiǎn)便起見,圖中只畫出了DDS3輸出的I、Q兩路信號(hào)中的一路,這不影響對(duì)信號(hào)控制時(shí)序的理解。

為了便于信號(hào)處理,該系統(tǒng)對(duì)各路DDS輸出信號(hào)的時(shí)間關(guān)系提出了嚴(yán)格的要求:(1)相位檢波器的兩路正交參考信號(hào)相位應(yīng)嚴(yán)格控制在90°相差上,以保證正交檢波器的性能。(2)其初始相位可以通過計(jì)算機(jī)控制調(diào)整。(3)DDS2的輸出信號(hào)和DDS3的I支路輸出信號(hào)必須同步,以保證在DDS3同相支路上的信號(hào)相位與中頻信號(hào)的相位保持同步;同時(shí)Q路信號(hào)必須保持相位的正交。(4)每個(gè)射頻脈沖周期,各路DDS輸出信號(hào)的初始相位嚴(yán)格同步,保證回波信號(hào)的相參積累。

2 多路同步設(shè)計(jì)

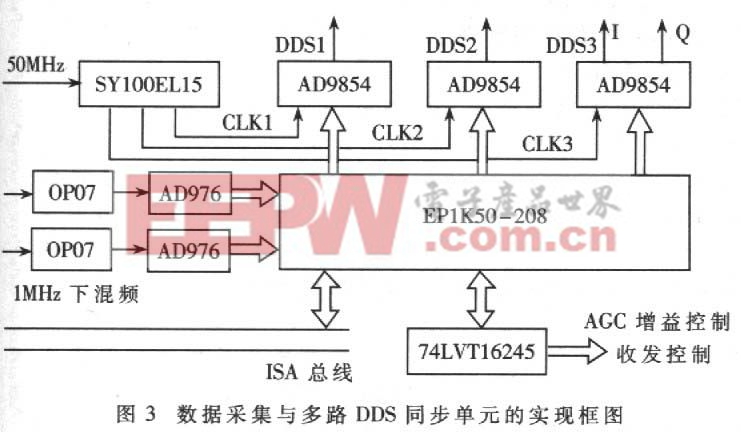

圖3是該自動(dòng)測(cè)試系統(tǒng)的數(shù)據(jù)采集、多路DDS同步單元的實(shí)現(xiàn)框圖。經(jīng)過相位檢波、低通濾波的I、0兩路信號(hào)輸入到該單元電路中,經(jīng)OP-07放大、AD976采集后,再經(jīng)FPGA由ISA總線送入到計(jì)算機(jī)中。OP-07具有低偏移、高開環(huán)增益的特點(diǎn),適合于高增益的測(cè)試系統(tǒng)應(yīng)用。AD976是采樣速率為200ksps的高速16位低功耗模數(shù)轉(zhuǎn)換器。FPGA芯片采用Ahera公司的ACEX系列芯片EPlK50,實(shí)現(xiàn)ISA總線與三路DDS及數(shù)據(jù)采集的接口。其靈活的可重新配置特性為實(shí)現(xiàn)接口電路提供了極大的方便,片上集成有4OKbit的RAM,便于緩存計(jì)算機(jī)的控制信息。DDS芯片選擇美國模擬器件公司的AD9854。它的相位累加器為48位,利用片上PLL可實(shí)現(xiàn)4~20倍的可編程倍頻,內(nèi)部最高時(shí)鐘可達(dá)300blHz,尤為突出的優(yōu)勢(shì)在于具有100MHz的高速并行配置接口,內(nèi)置最大相位誤差小于1°的I、Q兩路的DAC輸出,便于產(chǎn)生lMHz的正交信號(hào)。對(duì)于該自動(dòng)測(cè)試系統(tǒng),各路DDS之間的同步關(guān)系是電路設(shè)計(jì)的核心問題。AD9854芯片本身沒有同步信號(hào),要實(shí)現(xiàn)各路的精確同步,必須對(duì)電路進(jìn)行優(yōu)化設(shè)計(jì)。為分析方便,分別從參考時(shí)鐘、刷新時(shí)鐘和內(nèi)部鎖相倍頻三部分進(jìn)行討論。

評(píng)論