基于ADV7125的嵌入式系統VGA接口設計

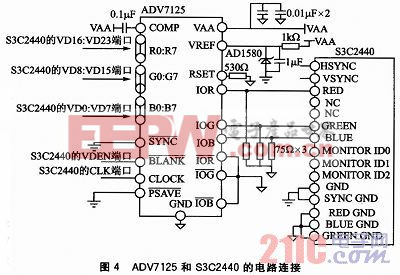

3.2 S3C2440和ADV7125的電路連接

設計中主要使用S3C2440處理器的LCD控制器接口,它主要通過DMA方式占用系統總線,支持彩色TFT液晶屏,支持16 bbp無調色真彩。 LCD接口數據的低8位,中間8位和高8位分別與ADV7125芯片的BLUE信號、GREEN信號和RED信號相連,這樣就完成了S3C2440處理器與ADV7125芯片之間數字信號的傳輸。ADV7125芯片的時鐘信號采用LCD接口的時鐘信號,

3.3 電路連接需要注意的問題

ADV7125可以用于灰度視頻信號輸出。例如:僅用于1個通道進行視頻輸出,這時其他兩個不用的視頻數據信道都應該與邏輯0相連,不用的模擬輸出應該與使用的信道一樣連接相同的負載。

為了實現ADV7125的最優噪聲性能,對PCB的設計必須特別注意。ADV7125電源和地線上的噪聲應該優化。可以通過屏蔽數字輸入和提供好的退耦達到這一點。VAA和GND的引線長度應該盡量短,這樣可以減小電感環路。在設計PCB時應盡量把模擬地與數字地分開,地線應該通過1個磁珠與PCB大面積鋪地相連,并且磁珠應該盡可能的靠近ADV7125器件的地引腳。電路中使用的電容應該盡可能的靠近對應引腳,并且電容的引線應該盡可能的短,這樣可以減小引線電容。由于使用頻率非常高,時鐘引線應盡可能地短,這樣可以減小噪聲的抖動。視頻輸出信號應該由數字地平面覆蓋,這樣可以增大高頻電源抑制比。

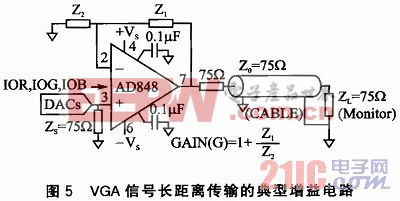

由于模擬RGB信號采用高阻電流源輸出方式,可以直接驅動75 Ω的同軸傳輸線。長于10 m的電纜可能會對高頻模擬輸出脈沖衰減。使用輸出緩沖可以補償電纜的失真。這些緩沖器在整個輸出電壓擺幅期間,必須有足夠的電流。常見的有AD84x系列的單片運放。在較高的頻率下(如80 MHz),推薦使用AD848。其典型增益電路如圖5所示。

通過簡單的計算可以得知其增益為:GAIN=1+Z1/Z2。改變緩沖電路的增益器件Z1、Z2來滿足所要求的視頻電平。

3.4 相關的軟件設置

下面以簡單的測試程序為例來說明相關軟件的編寫。

軟件設計的基本流程如圖6所示。具體過程如下:

①首先對LCD的功能寄存器進行初始化,主要設置LCD控制寄存器1~5,LCD緩沖區起始地址控制寄存器;屏蔽LCD中斷。

②其次對LCD的輸出時序(VGA信號時序)進行設置。設置分辨率、周期、前(后)信號、同步脈沖。

③再次是對視頻信號進行設置,主要是使能LCD視頻信號的輸出。

④用一幅圖像的輸出來測試VGA的顯示是否正常。

評論