基于SOPC的車輛息線控制器設計方案

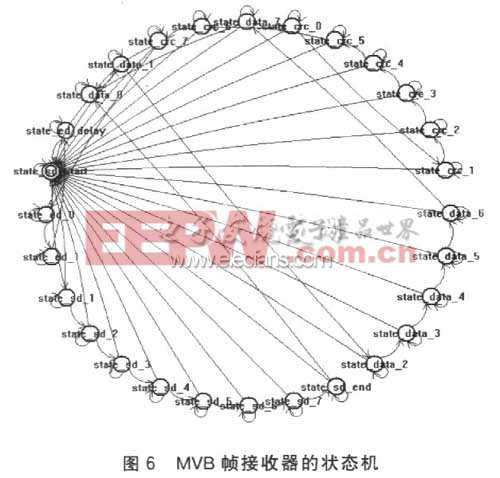

接收器實現的關鍵是有效數據幀的識別,實現思路類似于發送器,根據編碼校驗可以實現。另一個問題是與總線的接口方式,本設計采用了8位并行數據寬度輸出,加序號標識的方法可以接收任意給定長度的有效數據。接收器的狀態機如圖6所示。

2.4 Avalon總線接口

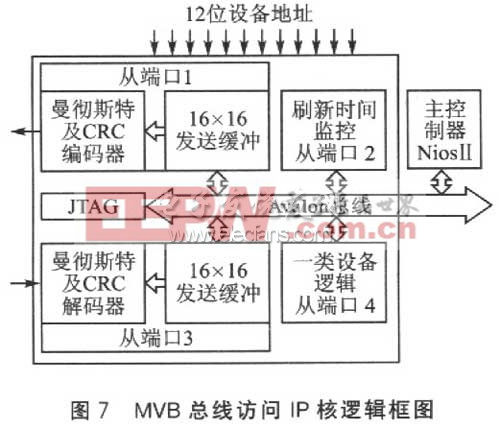

采用Altera公司開發的Avalon交互式片上系統總線作為本總線訪問IP核的內聯總線,連接IP核內各個模塊。如圖7所示,總線訪問IP核結構包括:編碼器模塊、解碼器模塊、宿端口刷新時間監控模塊、一類設備邏輯控制模塊。總線訪問IP核內共有4個Avalon從端口,其中NiosII主控制器上設置了一個Avalon總線主端口,其他各個模塊上面均設置了Avalon總線從端口,由主控制器控制總線上的數據流傳輸實現各個模塊的協同工作,其邏輯框圖如圖7所示。

3.1 總線訪問IP核與NiosII的系統集成

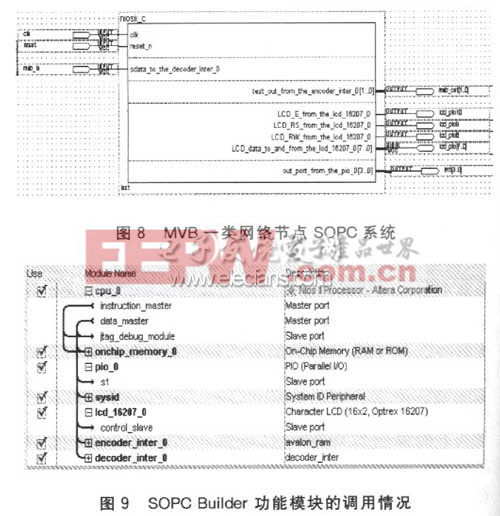

利用QuartersII的SOPC Builder工具,集成了1個32位NiosII軟核處理器、4 KB的片內RAM、MVB總線訪問IP核(包括編碼器和解碼器)以及LCD控制模塊,在Altera的CycloneII FPGA上構成了一個能實現MVB一類網絡節點功能的片上系統,如圖8所示。圖9為SOPCBuilder中各個功能模塊的凋用情況。

評論