Virtex-II Pro開發板進行雙核系統解決方案

Xilinx Virtex-II Pro開發板為各大學主要采用的開發板,該板上主芯片XC2VP30內置兩個硬核PowerPC405,具有30 816邏輯單元、136個18位的乘法器、2 448 Kbit的Block RAM。國內研究應用多使用該板進行單核系統設計,未能充分利用其雙核資源。其原因在于:Xilinx公司軟件對Virtex-II系列開發板的雙核系統設計支持性不好;Virtex-II Pro開發板只具有一個串口輸出,給調試帶來了極大的不便。

本文引用地址:http://www.104case.com/article/150050.htm 針對在Virtex-II Pro開發板進行雙核系統設計難

度大的問題,本文給出雙核硬件系統的構建方法,提出一種共享串口輸出和共享存儲器的系統結構,能夠充分利用板上資源,下載調試非常便利,可以很好地支持雙核的應用設計。

1 硬件系統設計

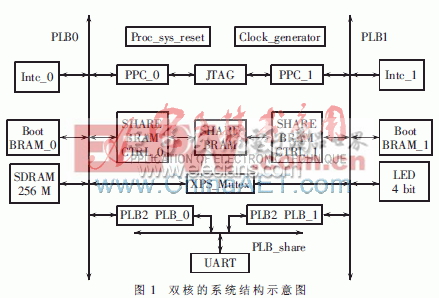

系統采用EDK10.1i03開發環境。設計雙核的系統硬件結構如圖1所示。

系統具有2個PowerPC405處理器:PPC_0和PPC_1,兩個處理器具有各自獨立的私有Boot BRAM,用于存儲相應的應用程序。PPC_0通過總線PLB_0控制外設SDRAM,PPC_1通過總線PLB1控制外設LED_4Bits。兩個處理器具有各自的中斷控制器和復位控制器。JTAG具有2個PowerPC的接口,并通過共享串口進行信息輸出。

雙核系統設計流程如下:

(1)利用BSB(Base system Builder)向導生成單核系統。

系統BSB設置的參數如下:

· System clock:100 MHz,no cache,no OCM

· RS232:opb UARTLITE,115200n8,use interrupt

· DDRAM:PLB DDR 256 MB,use interrupt

· LEDs_4 Bit:use interrupt

· PLB_BRAM_IF_CNTLR:64 KB

(2)添加和配置IP

由于EDK10不支持雙核系統設計,因此需要手動添加和配置相關IP,需添加的IP核有:

ppc405, plb_v46, plb2plb_bridge, bram_block, opb_intc plb_bram_if_cntlr, xps_mutex

MHS(Microprocessor Hardware Specification)是描述硬件結構的文件,需要修改MHS文件對添加的IP核進行配置。這里給出主要的ppc405、bram_block、xps_mutex核的配置說明,其他IP核將不再贅述。

①對PPC405_1的配置說明

BEGIN ppc405

PARAMETER INSTANCE = PPC_1

PARAMETER HW_VER = 3.00.a

PARAMETER C_DSOCM_DCR_BASEADDR=

0b0000100000

PARAMETER C_DSOCM_DCR_HIGHADDR =

0b0000100011

BUS_INTERFACE RESETPPC=ppc_rest_bus_1 //復位

BUS_INTERFACE JTAGPPC = jtagppc_cntlr_0_1

#用于PPC_1調試

BUS_INTERFACE IPLB0=plb1//總線

BUS_INTERFACE DPLB0=plb1

PORT EICC405EXTINPUTIRQ=xps_intc_1_Irq

PORT CPMC405CLOCK=proc_clk_s //時鐘

END

②對Mutex核進行配置

BEGIN xps_mutex

PARAMETER INSTANCE = xps_mutex_0

PARAMETER HW_VER = 1.00.a

PARAMETER C_NUM_MUTEX = 2

PARAMETER C_SPLB0_BASEADDR = 0x82400000

#該地址應用于Mutex初始化

PARAMETER C_SPLB0_HIGHADDR = 0x8240ffff

PARAMETER C_SPLB1_BASEADDR = 0x82600000

#該地址應用于Mutex初始化

PARAMETER C_SPLB1_HIGHADDR = 0x8260ffff

BUS_INTERFACE SPLB1 = plb1

BUS_INTERFACE SPLB0 = plb0

END

③共享BRAM核進行配置

BEGIN bram_block

PARAMETER INSTANCE = share_bram

PARAMETER HW_VER = 1.00.a

BUS_INTERFACE PORTB=share_bram_if_cntlr_1_PORTA

BUS_INTERFACE PORTA = share_bram_if_cntlr_0_

PORTA

END

(3)生成地址空間(Generate Addresses)

使用Generate Addresses命令,系統自動分配地址空間。由于軟件本身不支持雙核系統設計,在地址空間沖突時,需要手動對沖突的地址空間進行調整。使用Generate Bitstream可產生系統的硬件比特流。

評論