基于并行流水結構的RS255/RS233譯碼器設計

由ME算法推導可知,使用脈動電路結構實現(xiàn)ME算法時,至多使用2級迭代電路即可降低R(x)多項式階數(shù)1階。因此,脈動電路結構采用32階流水結構電路即可保證迭代算法完成收斂得到最后結果。電路結構如圖4所示。

2.3 錢搜索和Forney算法

錢搜索模塊接收KES模塊的錯誤位置多項式信號δ(x),利用錢搜索算法逐個檢查符號位是否發(fā)生錯誤,輸出錯誤位置和錯誤位置多項式的奇數(shù)項之和,供EE模塊計算錯誤圖案和糾錯。

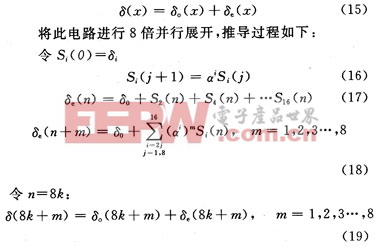

設錯誤位置多項式δ(x)可以表達為奇數(shù)項和偶數(shù)項之和:

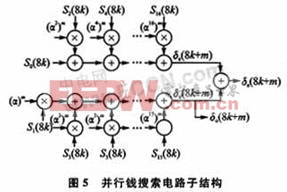

并行錢搜索電路子結構如圖5所示。圖中m表示并行模塊編號數(shù),m=1,2,…,8。所有的乘法器均是常數(shù)乘法器,8倍并行結構由圖5所示的8個同樣的結構組成。

EE(錯誤值計算)模塊根據(jù)CS模塊輸出的δodd(x)以及KES模塊輸出的ω(x)計算出錯誤圖案。

EE模塊需要求解w(ai),電路結構推導過程和求解δ(ai)的過程一樣,電路結構也基本相同,這里不再累述。

3 仿真驗證與綜合

上述譯碼器采用自頂向下的設計流程劃分模塊,用Verilog HDL完成RTL代碼的編寫,然后在Mentor公司的ModelSim SE 6.1b仿真驗證工具下編寫測試代碼進行仿真驗證。仿真結果如圖6所示,譯碼器能正確實現(xiàn)譯碼功能。

因本譯碼器可糾正16個錯誤,超過16個錯誤便不可糾正,在仿真時譯碼輸入樣本采用了2種:一種樣本不超過16個錯誤,另一種樣本超過16個錯誤。仿真結果表明,此譯碼器能在不超過16個錯誤的樣本下正常譯碼。

譯碼器在Quartus II 8.0上進行綜合和優(yōu)化,采用Altera公司Cyclone系列的EP2C15AF256C8芯片為目標器件。譯碼器的工作時鐘頻率可達85 MHz,數(shù)據(jù)吞吐率可達5 440 Mb/s,占用邏輯單元數(shù)為13 947個(片內(nèi)共14 448,占用率為97%),RAM占用16 698位(片內(nèi)共239 616位,占用率為7%)。譯碼器性能對比如表1所列。

與參考文獻[4]相比,由于本譯碼器采用了并行結構在增加了不到3倍的硬件資源的情況下,吞吐率時鐘比(吞吐率/時鐘)提高了8倍,而且縮短了3/4的澤碼延遲。與參考文獻[5]相比,本文所采用的譯碼器增加了不到3倍的硬件資源,提高了8倍的吞吐率時鐘比。由于參考文獻[5]采用串行譯碼結構,本文所采用的并行流水譯碼結構較串行譯碼結構縮減了19/20的譯碼延遲。本文引用地址:http://www.104case.com/article/149398.htm

評論