I2S總線概述

音響數據的采集、處理和傳輸是多媒體技術的重要組成部分。眾多的數字音頻系統已經進入消費市場,例如數字音頻錄音帶、數字聲音處理器。對于設備和生產廠家來說,標準化的信息傳輸結構可以提高系統的適應性。I2S(Inter—IC Sound)總線是飛利浦公司為數字音頻設備之間的音頻數據傳輸而制定的一種總線標準,該總線專責于音頻設備之間的數據傳輸,廣泛應用于各種多媒體系統。它采用了沿獨立的導線傳輸時鐘與數據信號的設計,通過將數據和時鐘信號分離,避免了因時差誘發的失真,為用戶節省了購買抵抗音頻抖動的專業設備的費用。

本文引用地址:http://www.104case.com/article/148633.htmI2S總線規范

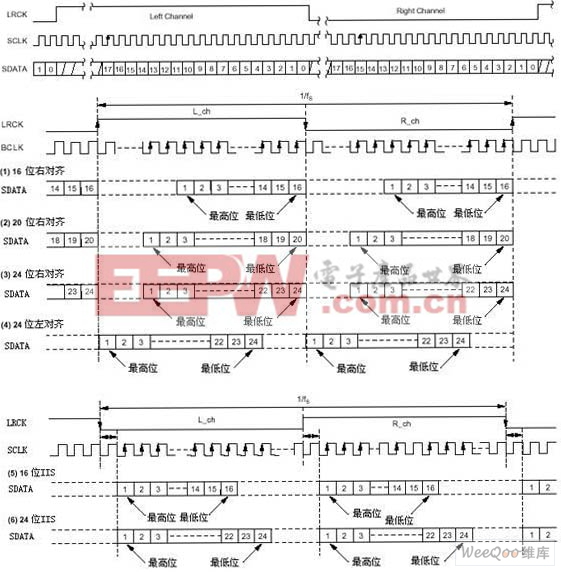

在飛利浦公司的I2S標準中,既規定了硬件接口規范,也規定了數字音頻數據的格式。I2S有3個主要信號:1.串行時鐘SCLK,也叫位時鐘(BCLK),即對應數字音頻的每一位數據,SCLK都有1個脈沖。SCLK的頻率=2×采樣頻率×采樣位數 2. 幀時鐘LRCK,用于切換左右聲道的數據。LRCK為“1”表示正在傳輸的是左聲道的數據,為“0”則表示正在傳輸的是右聲道的數據。LRCK的頻率等于采樣頻率。3.串行數據SDATA,就是用二進制補碼表示的音頻數據。

有時為了使系統間能夠更好地同步,還需要另外傳輸一個信號MCLK,稱為主時鐘,也叫系統時鐘(Sys Clock),是采樣頻率的256倍或384倍。

串行數據(SD)

I2S格式的信號無論有多少位有效數據,數據的最高位總是出現在LRCK變化(也就是一幀開始)后的第2個SCLK脈沖處。這就使得接收端與發送端的有效位數可以不同。如果接收端能處理的有效位數少于發送端,可以放棄數據幀中多余的低位數據;如果接收端能處理的有效位數多于發送端,可以自行補足剩余的位。這種同步機制使得數字音頻設備的互連更加方便,而且不會造成數據錯位。

隨著技術的發展,在統一的 I2S接口下,出現了多種不同的數據格式。根據SDATA數據相對于LRCK和SCLK的位置不同,分為左對齊(較少使用)、I2S格式(即飛利浦規定的格式)和右對齊(也叫日本格式、普通格式)。

為了保證數字音頻信號的正確傳輸,發送端和接收端應該采用相同的數據格式和長度。當然,對I2S格式來說數據長度可以不同。

字段(聲道)選擇(WS)

命令選擇線表明了正在被傳輸的聲道。

WS=0,表示正在傳輸的是左聲道的數據。

WS=1,表示正在傳輸的是右聲道的數據。

WS可以在串行時鐘的上升沿或者下降沿發生改變,并且WS信號不需要一定是對稱的。在從屬裝置端,WS在時鐘信號的上升沿發生改變。WS總是在最高位傳輸前的一個時鐘周期發生改變,這樣可以使從屬裝置得到與被傳輸的串行數據同步的時間,并且使接收端存儲當前的命令以及為下次的命令清除空間。

電氣規范:

輸出電壓:

VL 0.4V

VH>2.4V

輸入電壓

VIL=0.8V

VIH=2.0V

注:目前使用的TTL電平標準,隨著其他IC(LSI)的流行,其他電平也會支持。

時序要求:

在I2s總線中,任何設備都可以通過提供必需的時鐘信號成為系統的主導裝置,而從屬裝置通過外部時鐘信號來得到它的內部時鐘信號,這就意味著必須重視主導裝置和數據以及命令選擇信號之間的傳播延遲,總的延遲主要由兩部分組成:

外部時鐘和從屬裝置的內部時鐘之間的延遲

內部時鐘和數據信號以及命令選擇信號之間的延遲

對于數據和命令信號的輸入,外部時鐘和內部時鐘的延遲不占據主導地位,它只是延長了有效的建立時間(set—up time)。延遲的主要部分是發送端的傳輸延遲和設置接收端所需的時間。

T是時鐘周期,Tr是最小允許時鐘周期,T>Tr這樣發送端和接收端才能滿足數據傳輸速率的要求。

對于所有的數據速率,發送端和接收端均發出一個具有固定的傳號空號比(mark—space ratio)的時鐘信號,所以t LC和tHC是由T所定義的。 t LC和tHC必須大于0.35T,這樣信號在從屬裝置端就可以被檢測到。

延遲(tdtr)和最快的傳輸速度(由Ttr定義)是相關的,快的發送端信號在慢的時鐘上升沿可能導致tdtr不能超過tRC而使thtr為零或者負。只有tRC不大于tRCmax的時候(tRCmax>:0.15T),發送端才能保證thtr大于等于0。

為了允許數據在下降沿被記錄,時鐘信號上升沿及T相關的時間延遲應該給予接收端充分的建立時間(set-up time)。

數據建立時間(set-up time)和保持時間(hold time)不能小于指定接收端的建立時間和保持時間。

I2S總線結構配置

隨著WS信號的改變,導出一個WSP脈沖信號,進入并行移位寄存器,從而輸出數據被激活。串行數據的默認輸入是0,因此所有位于最低位(LSB)后的數據將被設置為0。

隨著第一個WS信號的改變,WSP在SCK信號的下降沿重設計數器。在“1 out of n”譯碼器對計數器數值進行譯碼后,第一個串行的數據(MSB)在SCK時鐘信號的上升沿被存放進入B1,隨著計數器的增長,接下來的數據被依次存放進入B2到Bn中。在下一個WS信號改變的時候,數據根據WSP脈沖的變化被存放進入左(聲道)鎖存器或者右(聲道)鎖存器,并且將B2一Bn的數據清除以及計數器重設,如果有冗余的數據則最低位之后的數據將被忽略。注意:譯碼器和計數器(虛線內的部分)可以被一個n比特移位寄存器所代替。

IIS總線接口可作為一個編碼解碼接口與外部8/16位的立體聲音頻解碼電路(CODEC IC)相連,從而實現微唱片和便攜式應用。它支持IIS數據格式和MSB-Justified 數據格式。IIS總線接口為先進先出隊列FIFO的訪問提供DMA傳輸模式來取代中斷模式,可同時發送和接收數據,也可只發送或接收數據。

評論