基于DSP的嵌入式數字攝像夜間能見度測量系統

2.2 嵌入式信號處理系統硬件設計

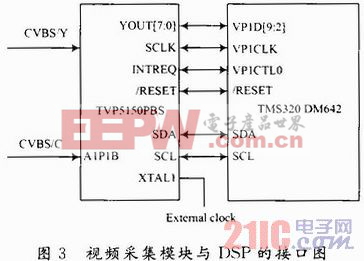

2.2.1 視頻采集模塊

采用8位模擬工業攝像機直接攝取PAL制的視頻圖像,送入視頻解碼器。解碼后輸出ITU-R BT.656格式數據。解碼器采用高性能、封裝小(32腳TQFP)、功耗小(小于150 mW)的TVP5150PBS,將PAL視頻信號轉換成數字色差信號(YUV 4:2:2)。圖3為視頻解碼模塊與DSP接口圖。本文引用地址:http://www.104case.com/article/148445.htm

在外部視頻輸入(0~1 Vpp)與TVP5150PBS視頻輸入之間設計分壓電阻網絡來使得TVP5150PBS的輸入電平為0~0.75 Vpp。

系統設置視頻口VP1的A通道作為視頻輸入口。TMS320DM642的I2C接口實現對TVP5150芯片內部寄存器的初始化和配置。TVP5150芯片的SCL,SDA引腳分別與TMS320DM642時鐘、數據地址線相連,通過SCL,SDA的時序配合完成DSP向視頻解碼器芯片寄存器寫入和讀出數據。TVP5 150接收攝像機的視頻信息,經過解碼后的數據串行輸出。數字視頻流包含奇偶場指示信號FI、場同步信號、行同步信號、像素時鐘、YUV數據輸出等元素,數據率約165 Mb/s。

2.2.2 圖像處理模塊

系統采用TI公司的面向數字媒體應用的32位定點DSP芯片TMS320DM642完成信號處理的過程。TVP5150輸出的BT.656視頻流經過TMS320DM 642的視頻口后存入2 560 B的VP1A通道FIFO。由于圖像數據量大,需要外擴片外存儲器用于存放圖像數據信息。通過EDMA通道把FIFO中的數據搬入片外存儲器SDRAM。當視頻口VP1的A通道出現視頻Y,U,V分量數據搬運請求后,在程序中便會觸發EDMA處理函數,完成FIFO數據向SDRAM的搬運。VP1EVTYA,VP1EVTUA,VP1EVTVA分別為發生在VP1A通道上與視頻Y,U,V分量相關的事件,與DM642 EDMA對應通道相連。當FIFO向SDRAM搬運完數據后運行在FLASH中的程序開始調用圖像數據,進行算法處理,求取光源和黑體的亮度值,完成能見度的計算。

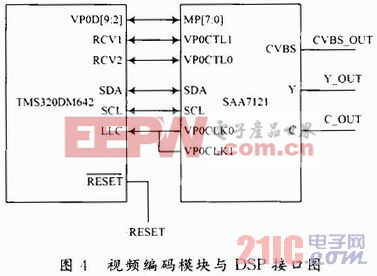

2.2.3 視頻顯示模塊

視頻顯示部分通過視頻編碼芯片把BT.656格式的視頻數據轉化為PAL制式的視頻信號,然后送入監視器顯示處理后的目標光源和目標黑體圖像。采用SAA7121H編碼器,將TMS320DM642的VP0 A通道設置為視頻輸出口。圖4為視頻編碼模塊與DSP連接圖,CVBS_OUT為解碼輸出的復合視頻。與TVP5150一樣,SAA7121芯片內部各個寄存器的配置通過TMS320DM642的I2C接口配置,且可以與TVP5150共用TMS320DM642的I2C總線。

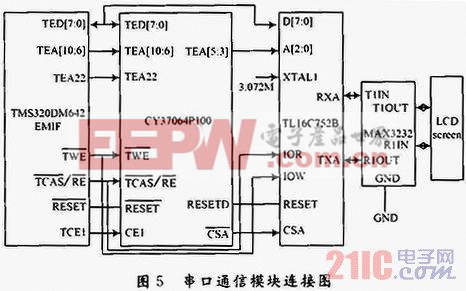

2.2.4 串口通信模塊

系統在DSP外部通過CY37064P100和TL16C752B擴展串口通信電路實現主芯片與帶串口液晶屏之間的通信,將夜間能見度值顯示在液晶屏上。圖5為串口通信模塊設計圖。選擇串口液晶屏實現能見度數值的顯示和歷史曲線的繪制。

接地電阻相關文章:接地電阻測試方法

評論