基于微處理器的嵌入式配置模式

3 被動并行異步配置

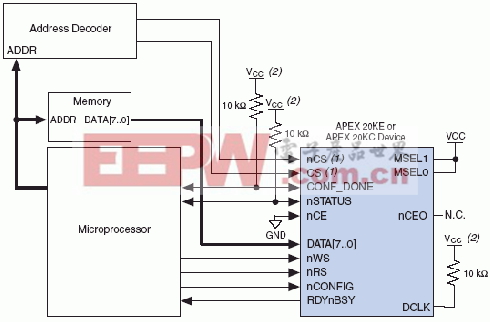

如同被動串行配置一樣,被動并行異步配置也包括三個階段:復位、配置和初始化。被動并行異步配置電路圖如圖3所示。當nSTATUS或者nCONFIG為低電平時,器件處于復位狀態。微處理器在nCONFIG管腳產生一個由低到高的跳變啟動FPGA的配置。當nCONFIG變高后,器件脫離復位狀態,并且釋放漏極開路的nSTATUS管腳,FPGA準備接收配置數據,配置階段開始。在配置階段,微處理器FPGA當作存儲器,進行寫操作,即微處理器先使片選有效,然后把8比特數據送到Data[0:7]管腳上,并配置管腳RDYnBSY到低電平,表示FPGA正忙于處理配置數據,微處理器可執行其它功能。在RDYnBSY低電平期間,FPGA使用內部振蕩器時鐘處理配置數據。當FPGA準備接收下一字節的配置數據時,它驅動RDYnBSY到高電平。微處理器檢測到這一高電平,便送下一字節數據到配置管腳。為了節省一根用來檢測RDYnBSY的I/O線,可采用讀存儲器的方法讀FPGA,其中nRS為存儲器讀信號,在nRS有效期間,RDYnBSY信號被送到數據線D7上。也可以不檢測RDYnBSY,也不讀FPGA,簡單地等待延時tBUSY(max)+tRDY2WS+tW2SB之后就寫下一個配置數據字節。FPGA每處理一字節配置數據后,若發現錯誤就會將nSTATUS拉低,暗示配置出錯。微處理器可以檢測這一錯誤,并重新進行配置。如同被動串行配置一樣,FPGA在正確接收所有配置數據后,將釋放CONF_DONE信號,于是該管腳被外部上拉電阻拉高,表示配置結束,初始化開始。

4 配置數據文件的生成

Altera的MAX+PLUS II或Quartus II開發工具可以生成多種格式的配置文件,用于不同配置方法。不同目標器件,配置數據的大小不同。配置文件的大小一般由二進制文件(擴展名為.rbf)決定。Altera提供的軟件工具不自動生成.rbf文件,需要按照下面的步驟生成:①在MAX+PLUS II編譯狀態,選擇文件菜單中的變換SRAM目標文件命令;②在變換SRAM目標文件對話框,指定要轉換的文件并且選擇輸出文件格式為.rbf(Sequential),然后予以確定。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論